- 您現在的位置:買賣IC網 > PDF目錄383298 > M393T2950CZA-CD5 (SAMSUNG SEMICONDUCTOR CO. LTD.) DDR2 Registered SDRAM MODULE 240pin Registered Module based on 512Mb C-die 72-bit ECC PDF資料下載

參數資料

| 型號: | M393T2950CZA-CD5 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | DDR2 Registered SDRAM MODULE 240pin Registered Module based on 512Mb C-die 72-bit ECC |

| 中文描述: | 注冊的DDR2 SDRAM內存模塊240針腳注冊模塊的512MB的基于C -死72位ECC |

| 文件頁數: | 10/21頁 |

| 文件大小: | 476K |

| 代理商: | M393T2950CZA-CD5 |

Rev. 1.2 Aug. 2005

512MB, 1GB, 2GB Registered DIMMs

DDR2 SDRAM

V

DDQ

V

IH

(AC) min

V

IH

(DC) min

V

REF

V

IL

(DC) max

V

IL

(AC) max

V

SS

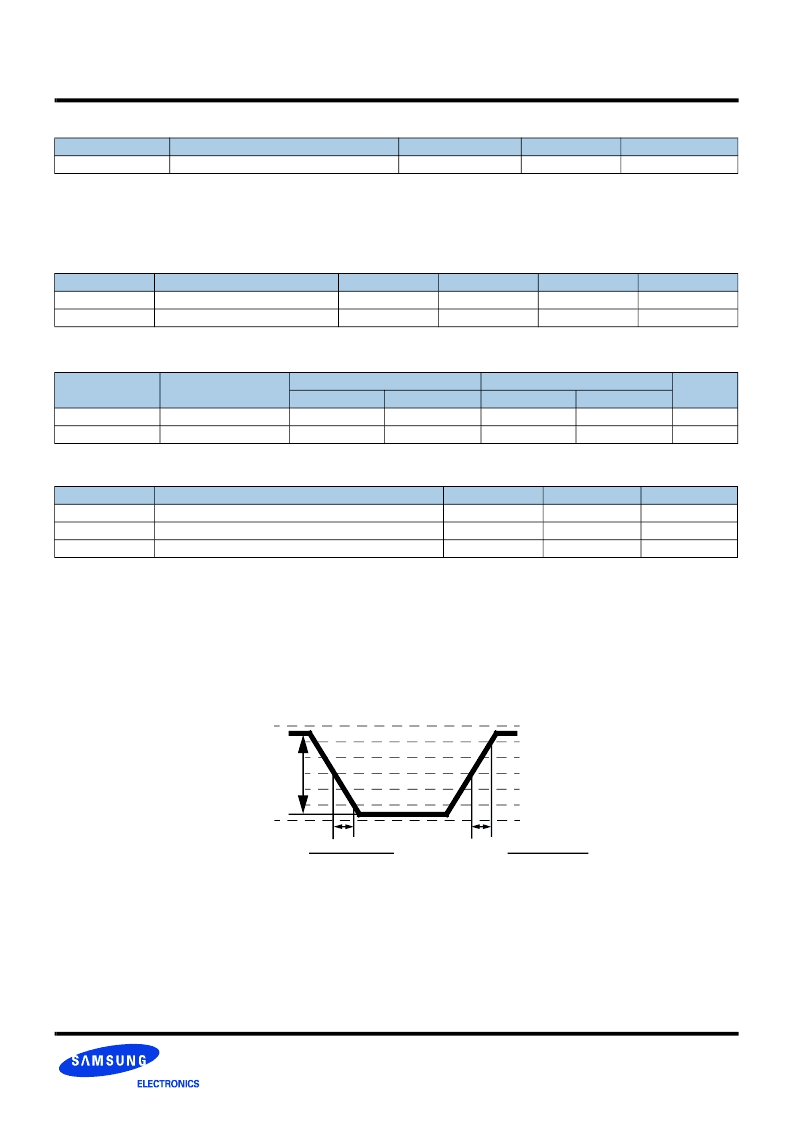

< AC Input Test Signal Waveform >

V

SWING(MAX)

delta TR

delta TF

V

REF

- V

IL

(AC) max

delta TF

Falling Slew =

Rising Slew =

V

IH

(AC) min - V

REF

delta TR

Operating Temperature Condition

Note :

1. Operating Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51.2

standard.

2. At 85 - 95 ×C operation temperature range, doubling refresh commands in frequency to a 32ms period ( tREFI=3.9 us ) is required, and to enter to self

refresh mode at this temperature range, an EMRS command is required to change internal refresh rate.

Input DC Logic Level

Input AC Logic Level

AC Input Test Conditions

Notes:

1. Input waveform timing is referenced to the input signal crossing through the V

IH/IL

(AC)

level applied to the device under test.

2. The input signal minimum slew rate is to be maintained over the range from V

REF

to V

IH

(AC) min for rising edges and the range from V

REF

to V

IL

(AC)

max for falling edges as shown in the below figure.

3. AC timings are referenced with input waveforms switching from V

IL

(AC) to V

IH

(AC) on the positive transitions and V

IH

(AC) to V

IL

(AC) on the negative

transitions.

Symbol

Parameter

Rating

Units

Notes

TOPER

Operating Temperature

0 to 95

°

C

1, 2, 3

Symbol

Parameter

Min.

Max.

Units

Notes

V

IH

(DC)

V

IL

(DC)

DC input logic high

V

REF

+ 0.125

- 0.3

V

DDQ

+ 0.3

V

REF

- 0.125

V

DC input logic low

V

Symbol

Parameter

DDR2-400, DDR2-533

DDR2-667, DDR2-800

Units

Min.

Max.

Min.

Max.

V

IH

(AC)

V

IL

(AC)

AC input logic high

V

REF

+ 0.250

-

-

V

REF

+ 0.200

V

AC input logic low

V

REF

- 0.250

V

REF

- 0.200

V

Symbol

Condition

Value

Units

Notes

V

REF

Input reference voltage

0.5 * V

DDQ

1.0

V

1

V

SWING(MAX)

SLEW

Input signal maximum peak to peak swing

V

1

Input signal minimum slew rate

1.0

V/ns

2, 3

相關PDF資料 |

PDF描述 |

|---|---|

| M393T5750CZA-CD5 | DDR2 Registered SDRAM MODULE 240pin Registered Module based on 512Mb C-die 72-bit ECC |

| M393T5750CZ3-CCC | 40 characters x 2 Lines, 5x7 Dot Matric Character and Cursor |

| M393T2953CZ3-CD5 | 40 Characters x 4 Lines, 5x7 Dot Matrix Character and Cursor |

| M393T2950CZ3-CD5 | 40 Characters x 4 Lines, 5x7 Dot Matrix Character and Cursor |

| M393T5750CZ3-CD5 | 40 Characters x 4 Lines, 5x7 Dot Matrix Character and Cursor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M393T2950CZA-CE6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR2 Registered SDRAM MODULE 240pin Registered Module based on 512Mb C-die 72-bit ECC |

| M393T2950CZA-CE7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR2 Registered SDRAM MODULE 240pin Registered Module based on 512Mb C-die 72-bit ECC |

| M393T2950EZA-CE600 | 制造商:Samsung Semiconductor 功能描述:512MSDDDRII_MDDR SDRAM MODULX72BOC(LF) - Bulk |

| M393T2950GZ3-CCC00 | 制造商:Samsung Semiconductor 功能描述:DIMM REG DDRII 400 CL3 1GIG SINGLE RANK 18/128MX4 SDRAMS - Trays |

| M393T2950GZA-CE600 | 制造商:Samsung Semiconductor 功能描述:DIMM 1GIGBYTE REGISTERED DDRII 667 CL5 SINGLE RANK 18/128MX4 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。