- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370955 > M38867M8A-A04HP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M38867M8A-A04HP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 45/110頁 |

| 文件大小: | 1601K |

| 代理商: | M38867M8A-A04HP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁

45

3886 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

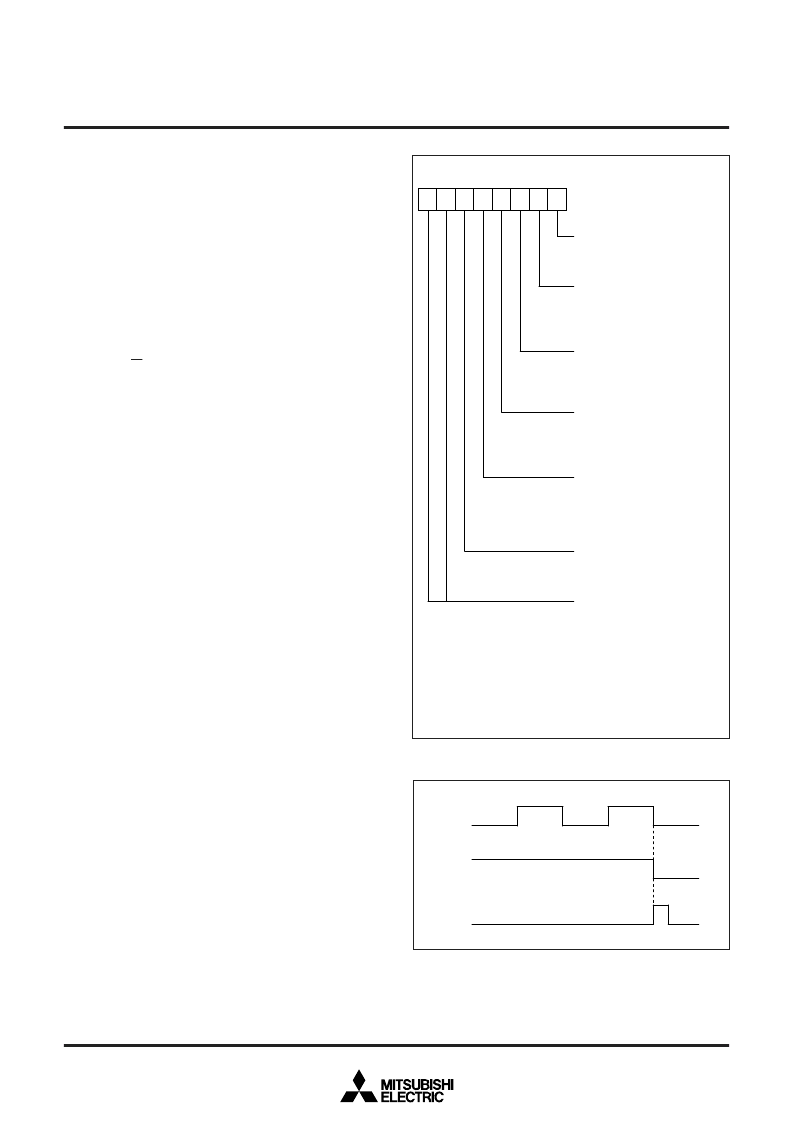

Fig. 40 Interrupt request signal generating timing

Fig. 39 Structure of I

2

C status register

Bit 6: Communication mode specification bit (transfer direc-

tion specification bit: TRX)

This bit decides a direction of transfer for data communication.

When this bit is “0,” the reception mode is selected and the data of

a transmitting device is received. When the bit is “1,” the transmis-

sion mode is selected and address data and control data are

output onto the S

DA

in synchronization with the clock generated on

the S

CL

.

This bit is set/reset by software and hardware. About set/reset by

hardware is described below. This bit is set to “1” by hardware

when all the following conditions are satisfied:

When ALS is “0”

In the slave reception mode or the slave transmission mode

When the R/W bit reception is “1”

This bit is set to “0” in one of the following conditions:

When arbitration lost is detected.

When a STOP condition is detected.

When writing “1” to this bit by software is invalid by the START

condition duplication preventing function

(Note)

.

With MST = “0” and when a START condition is detected.

With MST = “0” and when ACK non-return is detected.

At reset

Bit 7: Communication mode specification bit (master/slave

specification bit: MST)

This bit is used for master/slave specification for data communica-

tion. When this bit is “0,” the slave is specified, so that a START

condition and a STOP condition generated by the master are re-

ceived, and data communication is performed in synchronization

with the clock generated by the master. When this bit is “1,” the

master is specified and a START condition and a STOP condition

are generated. Additionally, the clocks required for data communi-

cation are generated on the SCL.

This bit is set to “0” in one of the following conditions.

Immediately after completion of 1-byte data transfer when arbi-

tration lost is detected

When a STOP condition is detected.

Writing “1” to this bit by software is invalid by the START condi-

tion duplication preventing function

(Note)

.

At reset

Note:

START condition duplication preventing function

The MST, TRX, and BB bits is set to “1” at the same time after con-

firming that the BB flag is “0” in the procedure of a START condition

occurrence. However, when a START condition by another master

device occurs and the BB flag is set to “1” immediately after the con-

tents of the BB flag is confirmed, the START condition duplication

preventing function makes the writing to the MST and TRX bits in-

valid. The duplication preventing function becomes valid from the

rising of the BB flag to reception completion of slave address.

b

7

M

S

T

b

0

R

I

2

C

(

S

s

:

t

a

a

t

d

u

d

s

r

e

r

e

s

g

s

i

s

0

t

0

e

1

r

1

4

1

6

)

L

a

s

t

: L

: L

r

e

c

e

s

s

i

v

b

b

e

i

i

b

=

=

i

t

(

“

0

“

1

N

”

”

o

t

e

)

0

1

a

a

t

t

t

t

G

(

N

e

n

e

t

e

: N

: G

r

)

a

o

e

l

c

a

l

l

d

e

t

e

c

t

i

n

g

f

l

a

g

o

0

1

n

g

e

e

n

r

a

e

l

r

c

a

a

l

l

c

l

a

d

l

e

l

t

d

e

e

c

t

t

e

e

c

d

t

e

d

S

(

l

a

o

0

1

v

t

e

e

:

:

)

A

A

a

d

d

r

e

s

s

c

o

m

p

a

r

i

s

o

n

f

l

a

g

N

d

d

d

d

r

r

e

e

s

s

s

s

d

a

i

g

s

a

r

e

g

e

r

e

m

e

e

m

n

e

t

n

t

A

(

r

b

o

0

1

i

t

t

r

e

a

)

t

o

e

i

o

n

l

o

s

t

d

e

t

e

c

t

i

n

g

f

l

a

g

N

: N

: D

t

t

e

d

e

c

t

e

e

d

c

t

e

d

t

I

2

C

r

e

-

u

B

e

U

s

0

1

S

t

:

:

i

i

n

t

t

o

i

t

e

r

f

a

c

e

i

n

t

e

r

r

u

p

t

q

b

I

N

e

s

n

r

i

n

s

r

u

t

u

p

t

r

u

r

e

p

q

t

u

r

e

e

s

q

t

u

i

e

s

s

s

t

u

e

d

e

e

r

d

B

u

s

:

:

b

B

B

u

s

u

u

y

s

s

f

f

b

l

a

e

u

g

e

s

y

0

1

r

C

s

o

p

m

e

0

0

1

1

m

i

f

: S

: S

: M

: M

u

c

n

a

l

l

i

i

c

o

v

v

s

s

a

n

e

e

t

t

t

i

o

b

r

t

r

r

r

n

i

t

e

a

r

t

s

c

n

e

r

a

m

e

s

c

n

o

d

e

c

0

1

0

1

i

t

a

a

a

a

i

v

m

e

s

e

t

e

m

m

m

i

t

o

d

o

o

m

e

d

d

o

i

e

e

d

e

e

i

v

m

e

T

R

X B

B P

I

N A

L A

A

S A

D

0 L

B

N

o

t

e

:

T

b

W

h

e

e

w

r

i

t

s

e

r

t

“

b

t

e

0

i

t

n

a

.

t

o

n

d

f

l

a

g

s

c

a

n

b

e

r

e

a

d

o

u

t

b

u

t

c

a

n

n

o

t

i

e

”

t

h

e

s

e

b

i

t

s

a

t

w

r

i

t

i

n

g

.

S

C

L

P

I

N

I

2

C

I

R

Q

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38867M8A-A06HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867M8A-A07HP | connectors |

| M38867M8A-A11HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38869FFAHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38869M8A-XXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38867M8A-A06HP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867M8A-A07HP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867M8A-A11HP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867M8A-XXXHP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867M8-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。