- 您現在的位置:買賣IC網 > PDF目錄370847 > M37702M2AXXXFP (Mitsubishi Electric Corporation) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數資料

| 型號: | M37702M2AXXXFP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機 |

| 文件頁數: | 19/59頁 |

| 文件大小: | 811K |

| 代理商: | M37702M2AXXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

19

MITSUBISHI MICROCOMPUTERS

M37702M2AXXXFP, M37702M2BXXXFP

M37702S1AFP, M37702S1BFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

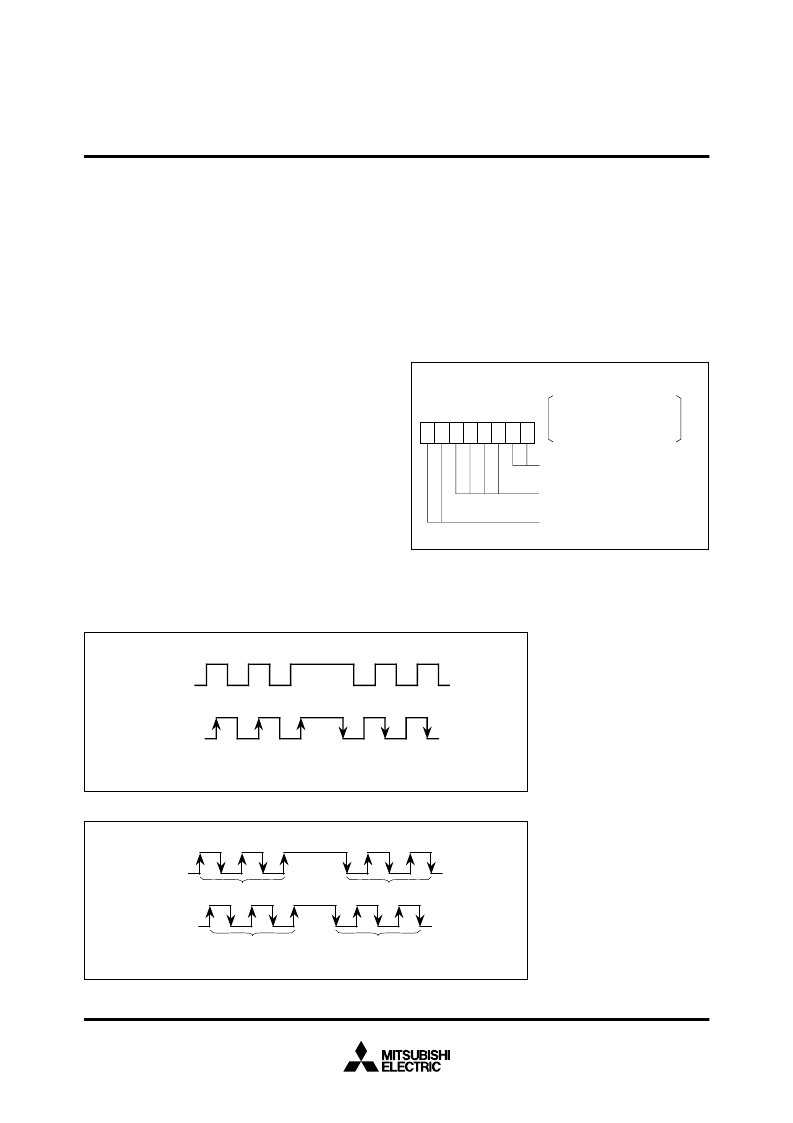

Fig. 19 Timer Aj mode register bit configuration when per-

forming two-phase pulse signal processing in event

counter mode

Data write and data read are performed in the same way as for

timer mode. That is, when data is written to timer Ai halted, it is

also written to the reload register and the counter. When data is

written to timer Ai which is busy, the data is written to the reload

register, but not to the counter. The counter is reloaded with new

data from the reload register at the next reload time. The counter

can be read at any time.

In event counter mode, whether to increment or decrement the

counter can also be determined by supplying two-phase pulse in-

put with phase shifted by 90° to timer A2, A3, or A4. There are two

types of two-phase pulse processing operations. One uses timers

A2 and A3, and the other uses timer A4. In either processing op-

eration, two-phase pulse is input in the same way, that is, pulses

out of phase by 90° are input at the TAj

OUT

(j = 2 to 4) pin and

TAj

IN

pin.

When timers A2 and A3 are used, as shown in Figure 17, the

count is incremented when a rising edge is input to the TAk

IN

pin

after the level of TAk

OUT

(k = 2, 3) pin changes from “L” to “H”, and

when the falling edge is inserted, the count is decremented.

For timer A4, as shown in Figure 18, when a phase related pulse

with a rising edge input to the TA4

IN

pin is input after the level of

TA4

OUT

pin changes from “L” to “H”, the count is incremented at

the respective rising edge and falling edge of the TA4

OUT

pin and

TA4

IN

pin.

When a phase related pulse with a falling edge input to the

TA4

OUT

pin is input after the level of TA4

IN

pin changes from “H” to

“L”, the count is decremented at the respective rising edge and

falling edge of the TA4

IN

pin and TA4

OUT

pin. When performing

this two-phase pulse signal processing, timer Aj mode register bit

0 and bit 4 must be set to “1” and bits 1, 2, 3, and 5 must be “0”.

Bits 6 and 7 are ignored. Note that bits 5, 6, and 7 of the up-down

flag register (44

16

) are the two-phase pulse signal processing se-

lection bit for timer A2, A3, and A4 respectively. Each timer

operates in normal event counter mode when the corresponding

bit is “0” and performs two-phase pulse signal processing when it

is “1”.

Count is started by setting the count start flag to “1”. Data write

and read are performed in the same way as for normal event

counter mode. Note that the direction register of the input port

must be set to input mode because two-phase pulse signal is in-

put. Also, there can be no pulse output in this mode.

Fig. 17 Two-phase pulse processing operation of timer A2 and timer A3

Fig. 18 Two-phase pulse processing operation of timer A4

TAk

OUT

TAk

IN

(k = 2, 3)

Increment-

count

Increment-

count

Increment-

count

Decrement-

count

Decrement-

count

Decrement-

count

Addresses

0 1 : Always “01” in event counter

mode

7 6 5 4 3 2 1 0

0

0 1

0 1 0 0 : Always “0100” when processing

two-phase pulse signal

Timer A2 mode register 58

16

Timer A3 mode register 59

16

Timer A4 mode register 5A

16

1 0 0

: Not used in event counter mode

TA4

OUT

TA4

IN

Increment

-

count at each edge

Decrement

-

count at each edge

Increment

-

count at each edge

Decrement

-

count at each edge

相關PDF資料 |

PDF描述 |

|---|---|

| M37702M2A-278FP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2A-XXXFP | DIODE SCHOTTKY DUAL SERIES 50V 150mW 0.41V-vf 70mA-IFM 1mA-IF 0.1uA-IR SOT-523 3K/REEL |

| M37702M2B-XXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2BXXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2L-249HP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M37702M2A-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2BXXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2B-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2L249HP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復。