- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370847 > M37560M6-XXXGP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37560M6-XXXGP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 44/65頁 |

| 文件大小: | 955K |

| 代理商: | M37560M6-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

7560 Group

44

Watchdog Timer

The watchdog timer gives a mean of returning to the reset status

when a program cannot run on a normal loop (for example, be-

cause of a software runaway).

The watchdog timer consists of an 8-bit watchdog timer L and a 6-

bit watchdog timer H. At reset or writing to the watchdog timer

control register (address 0037

16

), the watchdog timer is set to

“

3FFF

16

.

”

When any data is not written to the watchdog timer con-

trol register (address 0037

16

) after reset, the watchdog timer is in

stop state. The watchdog timer starts to count down from

“

3FFF

16

”

by writing an optional value into the watchdog timer control regis-

ter (address 0037

16

) and an internal reset occurs at an underflow.

Accordingly, programming is usually performed so that writing to

the watchdog timer control register (address 0037

16

) may be

started before an underflow. The watchdog timer does not function

when an optional value has not been written to the watchdog timer

control register (address 0037

16

). When address 0037

16

is read,

the following values are read:

G

value of high-order 6-bit counter

G

value of STP instruction disable bit

G

value of count source selection bit.

When bit 6 of the watchdog timer control register (address 0037

16

)

is set to

“

0,

”

the STP instruction is valid. The STP instruction is

disabled by rewriting this bit to

“

1.

”

At this time, if the STP instruc-

tion is executed, it is processed as an undefined instruction, so

that a reset occurs inside.

This bit cannot be rewritten to

“

0

”

by programming. This bit is

“

0

”

immediately after reset.

The count source of the watchdog timer becomes the system

clock

φ

divided by 8. The detection time in this case is set to 8.19 s

at f(X

CIN

) = 32 kHz and 32.768 ms at f(X

IN

) = 8 MHz.

However, count source of high-order 6-bit timer can be connected

to a signal divided system clock by 8 directly by writing the bit 7 of

the watchdog timer control register (address 0037

16

) to

“

1.

”

The

detection time in this case is set to 32 ms at f(X

CIN

) = 32 kHz and

128

μ

s at f(X

IN

) = 8 MHz. There is no difference in the detection

time between the middle-speed mode and the high-speed mode.

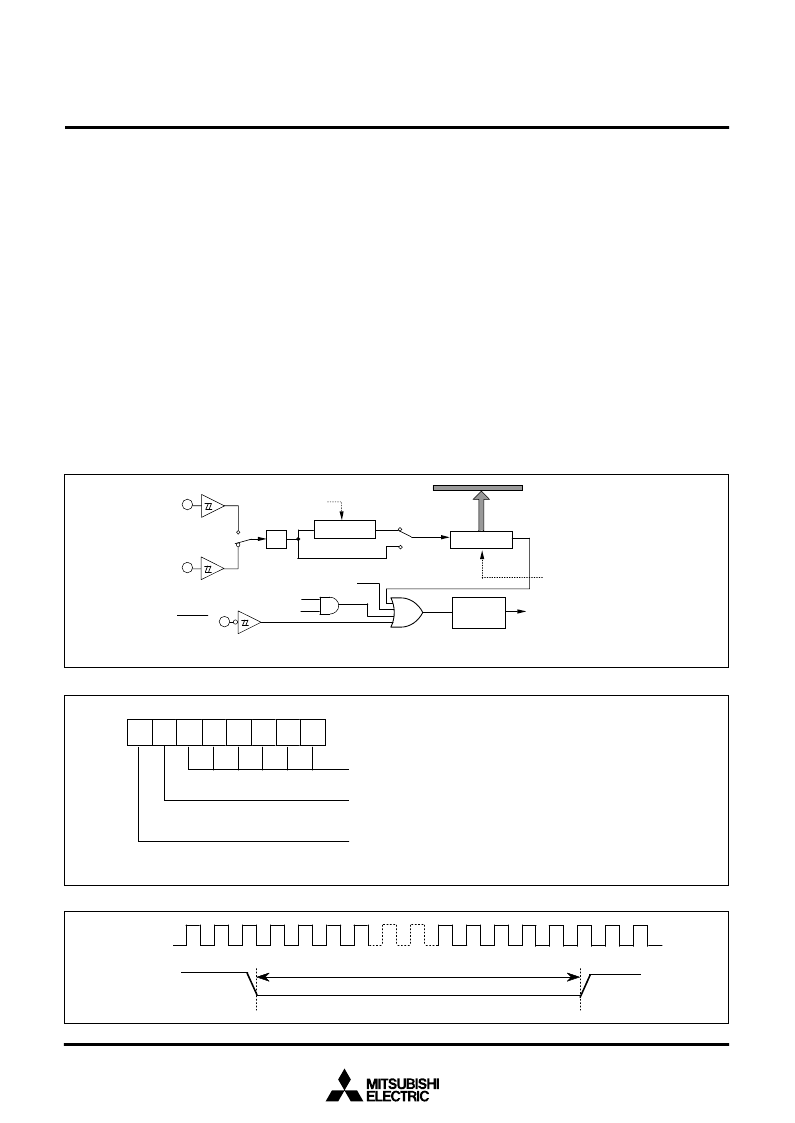

Fig. 45 Block diagram of watchdog timer

Fig. 46 Structure of watchdog timer control register

Fig. 47 Timing of reset output

X

IN

Data bus

X

CIN

“

1

”

“

0

”

Internal

system clock

selection bit

(Note)

“

0

”

“

1

”

1/16

Watchdog timer H count

source selection bit

Reset circuit

Undefined instruction

Reset

“

3F

16

”

is set when

watchdog timer is

written to.

Internal reset

RESET

Reset release time wait

“

FF

16

”

is set when

watchdog timer is

written to.

STP instruction

STP instruction disable bit

Watchdog timer

H (6)

Watchdog timer

L (8)

Note: This is the bit 7 of CPU mode register and is used to switch the middle-/high-speed mode and low-speed mode.

b

7

b

0

W

W

a

D

t

c

T

h

C

d

O

o

g

N

t

i

m

e

r

r

e

g

i

s

t

e

r

(

a

d

d

r

e

s

s

0

0

3

7

1

6

)

S

T

P

0

i

:

:

n

s

S

S

t

T

T

r

u

P

P

c

t

n

i

n

i

o

s

s

n

t

t

u

r

u

d

i

s

t

t

a

i

o

i

o

b

n

n

l

e

e

d

b

n

i

s

i

a

a

t

i

r

c

c

b

b

l

e

l

e

d

d

1

Watchdog timer H count source selecion bit

0 : Watchdog timer L underflow

1 : f(X

IN

)/16 or f(X

CIN

)/16

W

“

3

a

F

t

F

c

h

F

1

d

o

6

”

g

i

s

t

i

s

m

e

e

t

r

t

o

H

t

(

h

f

e

o

r

w

r

e

a

a

t

c

d

h

-

d

o

u

o

t

o

t

f

m

h

i

g

r

h

b

-

y

o

r

w

d

e

r

i

r

i

n

6

b

i

t

a

)

g

i

e

t

g

v

l

u

e

s

t

o

t

h

i

s

a

d

d

r

e

s

s

.

In

r

e

W

t

s

e

r

n

t

t

c

a

s

h

l

i

d

g

e

a

n

o

a

g

l

t

i

m

e

r

d

e

t

e

c

t

i

o

n

1

m

s

(

f

(

X

I

N

)

=

8

M

H

Z

)

f(

X

I

N

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37560M7-XXXFP | RES-ARRAY 39-OHM 4-ELEMENT 5% 0.063W CONVEX THK-FILM SMD-1206 TR-7-PA |

| M37560M8-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560M9-XXXFP | Thick Film Resistor Array; Series:CRB; Resistance:56kohm; Resistance Tolerance:+/- 5%; Power Rating:0.063W; Operating Temperature Range:-55 C to +125 C; Resistor Element Material:Thick Film; Voltage Rating:50VDC RoHS Compliant: Yes |

| M37560M9-XXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560MA-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37560M7A-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560M7A-XXXGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560M7D-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560M7D-XXXFS | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37560M7D-XXXGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。