- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45035 > M37545G8-XXXGP 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 PDF資料下載

參數(shù)資料

| 型號: | M37545G8-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| 封裝: | 7 X 7 MM, 0.80 MM PITCH, PLASTIC, LQFP-32 |

| 文件頁數(shù): | 31/63頁 |

| 文件大?。?/td> | 774K |

| 代理商: | M37545G8-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

Rev.1.07

Mar 19, 2009

Page 37 of 60

REJ03B0140-0107

7545 Group

MISRG

The 7545 Group has two power source supply pins. One is the

VCC pin, and the other is the VDDR pin only for RAM2. A

potential difference between VCC and VDDR may cause some

failures in reading from RAM2 o r wr iting to RAM2.

Accordingly, if there is a potential difference between VCC and

VDDR at power-on, confirm the bit 1 (RAM2 status flag) of

MISRG (address 003816) before reading from RAM2 or writing

to RAM2.

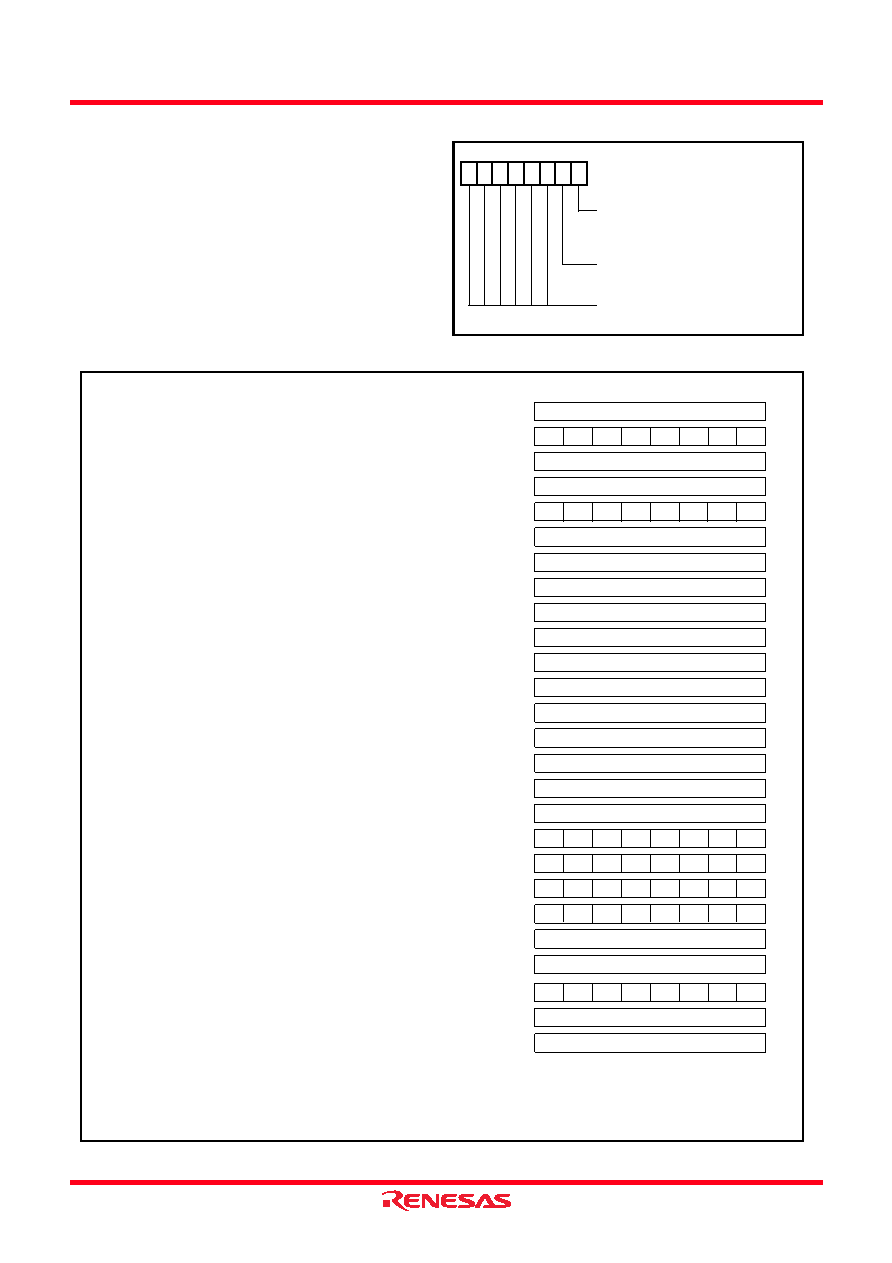

Fig. 39 Structure of MISRG

Fig. 40 Internal status of microcomputer at reset

b7

b0

RAM2 status flag

0: RW disabled

1: RW enabled

Oscillation stabilization time set bit after

release of the STP instruction

0: Set “0316” in timer1, and “FF16”

in prescaler 1 automatically

1: Not set automatically

Reserved bits

(Do not write “1” to these bits)

MISRG(address 003816, initial value: 0X16)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(12)

(13)

(14)

(15)

(16)(

17)

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

000116

000316

000516

000716

000916

001616

001716

001816

001916

002716

002816

002916

002A16

002B16

002C16

002D16

002E16

003816

003916

003A16

003B16

003C16

003E16

(PS)

(PCH)

(PCL)

0016

00

0016

FF16

0316

0016

0616

FF16

00

000

0

00

111

11

1

10

000

00

0

0016

X1

0016

00

0

FF16

00

000

00

0

Register contents

Address

Port P0 direction register (P0D)

Port P1 direction register (P1D)

Port P2 direction register (P2D)

Port P3 direction register (P3D)

Port P4 direction register (P4D)

Pull-up control register (PULL)

Port output mode switch register (PMOD)

Key-on wakeup pin selection register (KEYSEL)

Key-on wakeup edge selection register (KEYEDGE)

Carrier wave control register (CARCNT)

Prescaler 1 (PRE1)

Timer 1 (T1)

Timer count source set register (TCSS)

Timer 1, 2, 3 control register (TC123)

Timer 2 primary (T2P)

Timer 2 secondary (T2S)

Timer 3 (T3)

MISRG

Watchdog timer control register (WDTCON)

Interrupt edge selection register (INTEDGE)

CPU mode register (CPUM)

Interrupt request register 1 (IREQ1)

Interrupt control register 1 (ICON1)

Processor status register

Program counter

Contents of address FFFD16

Contents of address FFFC16

XX

X

XX

X

XX

X : Undefined

The content of other registers and RAM are undefined when the microcomputer is reset.

The initial values must be surely set before you use it.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37545GC-XXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| M37545G1KP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO32 |

| M37545G4GP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

| M37545G6KP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO32 |

| M37545G6-XXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37545GCGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GCKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GC-XXXGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GFGP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37545GFKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。