- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370845 > M37516 (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37516 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 32/54頁 |

| 文件大小: | 358K |

| 代理商: | M37516 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

32/54

M37516M6-XXXHP

GNOK-M37516M6-XXXHP-50

(MSETSU 2)

PA

GE

START/STOP

condition

control register

XXX11010

XXX11000

XXX00100

XXX01100

XXX01010

XXX00100

Oscillation

frequency

f(X

IN

) (MHz)

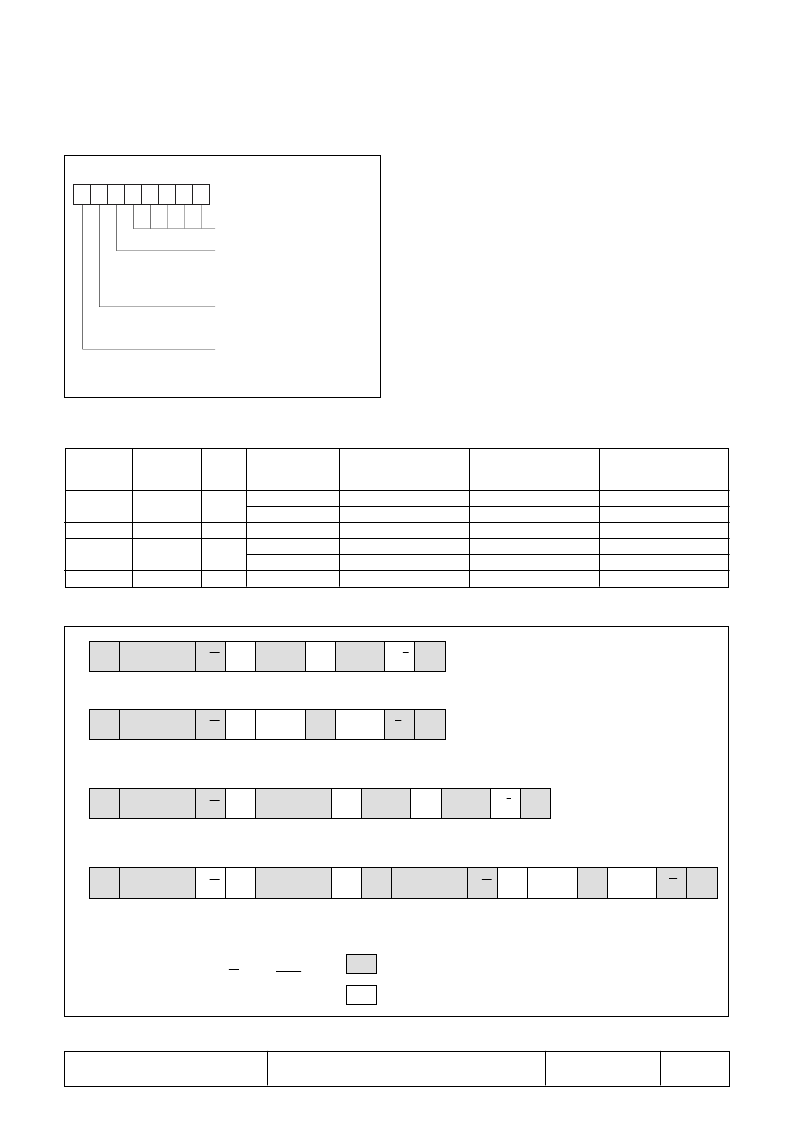

Fig. 35 Address data communication format

Fig. 34 Structure of I

2

C START/STOP condition control register

Note:

Do not set “00000

2

” or an odd number to the START/STOP condition set bit (SSC4 to SSC0).

Table 9 Recommended set value to START/STOP condition set bits (SSC4–SSC0) for each oscillation frequency

Main clock

divide ratio

System

clock

φ

(MHz)

SCL release time

(

μ

s)

Setup time

(

μ

s)

Hold time

(

μ

s)

8

8

4

2

2

8

2

2

3.375

μ

s (13.5 cycles)

3.125

μ

s (12.5 cycles)

2.5

μ

s (2.5 cycles)

3.25

μ

s (6.5 cycles)

2.75

μ

s (5.5 cycles)

2.5

μ

s (2.5 cycles)

6.75

μ

s (27 cycles)

6.25

μ

s (25 cycles)

5.0

μ

s (5 cycles)

6.5

μ

s (13 cycles)

5.5

μ

s (11 cycles)

5.0

μ

s (5 cycles)

3.375

μ

s (13.5 cycles)

3.125

μ

s (12.5 cycles)

2.5

μ

s (2.5 cycles)

3.25

μ

s (6.5 cycles)

2.75

μ

s (5.5 cycles)

2.5

μ

s (2.5 cycles)

4

1

2

1

S

Slave address R/W

A

Data

A/A

P

A

Data

7 bits

“0”

1 to 8 bits

1 to 8 bits

(1) A master-transmitter transnmits data to a slave-receiver

S

Slave address R/W

A

Data

A

P

A

Data

7 bits

“1”

1 to 8 bits

1 to 8 bits

(2) A master-receiver receives data from a slave-transmitter

7 bits

“0”

8 bits

(3) A master-transmitter transmits data to a slave-receiver with a 10-bit address

1 to 8 bits

1 to 8 bits

S

R/W

A

Slave address

1st 7 bits

Slave address

2nd bytes

A

A

Data

Data

P

A/A

7 bits

“0”

8 bits

(4) A master-receiver receives data from a slave-transmitter with a 10-bit address

S : START condition

A : ACK bit

Sr : Restart condition

P : STOP condition

R/W : Read/Write bit

7 bits

“1”

1 to 8 bits

1 to 8 bits

S

R/W

A

Slave address

1st 7 bits

Slave address

2nd bytes

A

Sr

Slave address

1st 7 bits

R/W

A

Data

Data

P

A

: Master to slave

: Slave to master

A

b7

b0

I

2

C START/STOP condition

control register

(S2D : address 0030

16

)

START/STOP condition set bit

SCL/SDA interrupt pin polarity

selection bit

0 : Falling edge active

1 : Rising edge active

SCL/SDA interrupt pin selection bit

0 : SDA valid

1 : SCL valid

Reserved

Do not write “1” to this bit.

SIS

SIP

SSC4 SSC3 SSC2 SSC1SSC0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37516M6-A30HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M6-A34HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M6-A40HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M6-A46HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M6-A48KP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37516E1H-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516E1-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516E1-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516E2H-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516E2-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。