- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370845 > M37481E8T (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M37481E8T |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁(yè)數(shù): | 58/97頁(yè) |

| 文件大小: | 1076K |

| 代理商: | M37481E8T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)當(dāng)前第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)

MITSUBISHI MICROCOMPUTERS

7480/7481 GROUP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

58

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

Table 13. Recommended operating conditions (cont.)

Symbol

Parameter

Standard values

Min.

Typ.

Max.

Unit

1

2

250

500

1

2

2.2V

CC

– 2

8

f(CNTR)

f(S

CLK

)

f(X

IN

)

f(X

IN

) = 4 MHz

f(X

IN

) = 8 MHz

f(X

IN

) = 4 MHz

f(X

IN

) = 8 MHz

f(X

IN

) = 4 MHz

f(X

IN

) = 8 MHz

V

CC

= 2.7 to 4.5 V

V

CC

= 4.5 to 5.5 V

MHz

kHz

MHz

MHz

Timer input frequency CNTR

0

(P4

0

),

CNTR

1

(P4

1

) (Note 3)

Clock input oscillation frequency (Note 3)

Serial I/O clock input

frequency S

CLK

(P1

6

)

(Note 3)

Clock synchronous

serial I/O mode

UART mode

Notes 1 :

–40 to 85 °C for extended operating temperature range version.

2 :

The average output currents I

OH

(avg) and I

OL

(avg) are the average values during 100 ms.

3 :

The clock input oscillation frequency is at 50 % duty ratio.

4 :

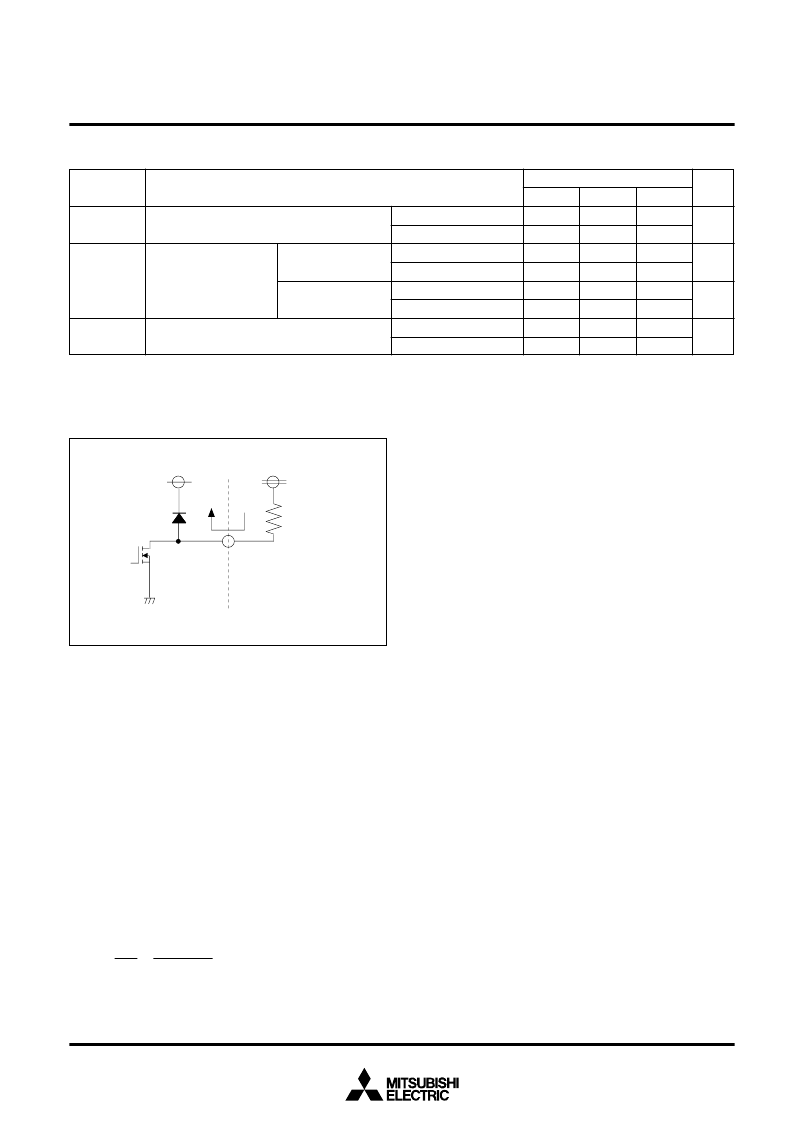

When applying a voltage through a resistor as shown in the figure 55, V

I

> V

CC

may be accepted if the current is 1 mA or less.

Fig. 55 Notes on use of ports P4 and P5

Notes on Clamp Diode (7481 Group)

(1) Total input current

The current of ports P4 and P5 through the clamp diode can

be drawn up to 1.0 mA per port. When a current that cannot be

consumed by microcomputer is sent flow to the clamp diode,

this may raise the power source pin voltage of the microcom-

puter.

The system power circuit must be designed so that the power

source voltage of the microcomputer may be stabilized within

the standard values.

(2) Maximum input voltage

If the input voltage of a signal connected to ports P4 and P5 is

beyond V

CC

+ 0.3 V, the input waveform should have a delay

exceeding 2 μs/V from the moment that this waveform goes

over the voltage.

For using a CR circuit for delay, calculate a proper delay value

by the following expression:

where V

IN

= Maximum input voltage amplitude margin and

t = C

R.

dt

dv

=

≥

2

10

–6

(s/V)

t

0.6

V

IN

Port P4, P5

I

VI

The clamp diode of the 7480/7481 group is designed for a level

shift of DC signal unlike ordinary switching diodes. Do not apply

sudden stress, such as rush current, directly to the diode.

Notes on Countermeasures for Noise and

Latch-up (7481 Group)

(1) Connect a bypass capacitor (0.1μF) across the V

CC

pin and

the V

SS

pin with the shortest possible wiring, using a relatively

thick wire.

(2) Connect a bypass capacitor (0.01 μF) across the V

REF

pin and

the V

SS

pin with the shortest possible wiring, using a relatively

thick wire.

(3) In the oscillation circuit, connect across the X

IN

and X

OUT

pins

with the shortest possible wiring. Connect the GND and V

SS

pins of the oscillation circuit with the shortest possible wiring,

using a relatively thick wire.

(4) In the case of the P3

3

/V

PP

pin of the built-in programmable

ROM version, connect an approximately 5 k

resistor to the

P3

3

/V

PP

pin the shortest possible in series.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37481MXT | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510E5156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510E6156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510E7156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510E8156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37481E8T-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:8-BIT SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 7470 SERIES |

| M37481E8T-XXXSP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37481E8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:8-BIT SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 7470 SERIES |

| M37481E8-XXXSP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37481M2T-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。