- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370828 > M2S56D20ATP75A (Mitsubishi Electric Corporation) 256M Double Data Rate Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M2S56D20ATP75A |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 256M Double Data Rate Synchronous DRAM |

| 中文描述: | 256M雙數(shù)據(jù)速率同步DRAM |

| 文件頁(yè)數(shù): | 20/40頁(yè) |

| 文件大小: | 768K |

| 代理商: | M2S56D20ATP75A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

20

MITSUBISHI ELECTRIC

Mar. '02

MITSUBISHI LSIs

DDR SDRAM

(Rev.1.44)

M2S56D20/ 30/ 40ATP -75AL, -75A, -75L, -75, -10L, -10

M2S56D20/ 30/ 40AKT -75AL, -75A, -75L, -75, -10L, -10

256M Double Data Rate Synchronous DRAM

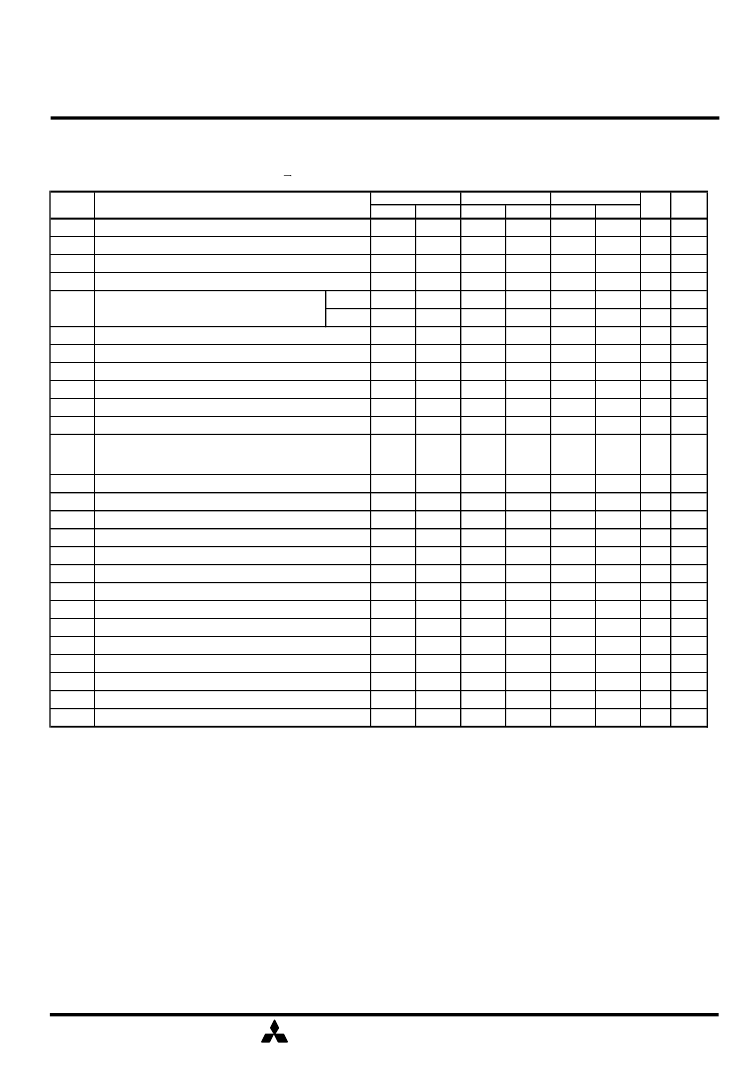

AC TIMING REQUIREMENTS

(Ta=0 ~ 70

o

C, VDD = VDDQ = 2.5V +0.2V, VSS = VSSQ = 0V, unless otherwise noted)

Min.

-0.75

Max

0.75

Min.

-0.75

Max

0.75

Min.

-0.8

Max

0.8

tAC

DQ Output Valid data delay time from CLK//CLK

ns

tDQSCK DQ Output Valid data delay time from CLK//CLK

-0.75

0.75

-0.75

0.75

-0.8

0.8

ns

tCH

CLK High level width

0.45

0.55

0.45

0.55

0.45

0.55

tCK

tCL

CLK Low level width

0.45

0.55

0.45

0.55

0.45

0.55

tCK

CL=2.5

7.5

15

7.5

15

8

15

ns

CL=2

7.5

15

10

15

10

15

ns

tDS

Input Setup time (DQ,DM)

0.5

0.5

0.6

ns

tDH

Input Hold time(DQ,DM)

0.5

0.5

0.6

ns

tDIPW

DQ and DM input pulse width (for each input)

1.75

1.75

2

ns

tHZ

Data-out-high impedance time from CLK//CLK

-0.75

0.75

-0.75

0.75

-0.8

0.8

ns

14

tLZ

Data-out-low impedance time from CLK//CLK

-0.75

0.75

-0.75

0.75

-0.8

0.8

ns

14

tDQSQ DQ Valid data delay time from DQS

0.5

0.5

0.6

ns

tHP

Clock half period

tCLmin

or

tCHmin

tCLmin

or

tCHmin

tCLmin

or

tCHmin

ns

tQH

Output DQS valid window

tHP-0.75

tHP-0.75

tHP-1.0

ns

tDQSS Write command to first DQS latching transition

0.75

1.25

0.75

1.25

0.75

1.25

tCK

tDQSH DQS input High level width

0.35

0.35

0.35

tCK

tDQSL DQS input Low level width

0.35

0.35

0.35

tCK

tDSS

DQS falling edge to CLK setup time

0.2

0.2

0.2

tCK

tDSH

DQS falling edge hold time from CLK

0.2

0.2

0.2

tCK

tMRD

Mode Register Set command cycle time

15

15

15

ns

tWPRES Write preamble setup time

0

0

0

ns

16

tWPST Write postamble

0.4

0.6

0.4

0.6

0.4

0.6

tCK

15

tWPRE Write preamble

0.25

0.25

0.25

tCK

tIS

Input Setup time (address and control)

0.9

0.9

1.1

ns

19

tIH

Input Hold time (address and control)

0.9

0.9

1.1

ns

19

tRPST Read postamble

0.4

0.6

0.4

0.6

0.4

0.6

tCK

tRPRE

Read preamble

0.9

1.1

0.9

1.1

0.9

1.1

tCK

-10

Unit

Notes

tCK

CLK cycle time

Symbol

AC Characteristics Parameter

-75A

-75

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2S56D30AKT | 256M Double Data Rate Synchronous DRAM |

| M2S56D30AKT-75A | 256M Double Data Rate Synchronous DRAM |

| M2S56D30AKT-75AL | 256M Double Data Rate Synchronous DRAM |

| M2S56D30AKT-75L | 256M Double Data Rate Synchronous DRAM |

| M2S56D30ATP | 256M Double Data Rate Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M2S56D20ATP-75A | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20ATP-75AL | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20ATP-75L | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20TP | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

| M2S56D20TP-10 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:256M Double Data Rate Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。