- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358970 > M24128-MN6T (意法半導(dǎo)體) 256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines PDF資料下載

參數(shù)資料

| 型號(hào): | M24128-MN6T |

| 廠商: | 意法半導(dǎo)體 |

| 元件分類: | DRAM |

| 英文描述: | 256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| 中文描述: | 一百二十八分之二百五十六千位串行IC總線的EEPROM芯片使能線無(wú) |

| 文件頁(yè)數(shù): | 7/17頁(yè) |

| 文件大?。?/td> | 135K |

| 代理商: | M24128-MN6T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

7/17

M24256, M24128

During the internal write cycle, the SDA input is

disabled internally, and the device does not re-

spond to any requests.

Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory discon-

nects itself from the bus, and copies the data from

its internal latches to the memory cells. The maxi-

mum write time (t

w

) is shown in Table 10, but the

typical time is shorter. To make use of this, an Ack

polling sequence can be used by the master.

The sequence, as shown in Figure 7, is:

– Initial condition: a Write is in progress.

– Step 1: the master issues a START condition

followed by a Device Select Code (the first byte

of the new instruction).

– Step 2: if the memory is busy with the internal

write cycle, no Ack will be returned and the mas-

ter goes back to Step 1. If the memory has ter-

will fit up to the end of the row, a condition known

as ‘roll-over’ occurs. Data starts to become over-

written (in a way not formally specified in this data

sheet).

The master sends from one up to 64 bytes of data,

each of which is acknowledged by the memory if

the WC pin is low. If the WC pin is high, the con-

tents of the addressed memory location are not

modified, and each data byte is followed by a

NoAck. After each byte is transferred, the internal

byte address counter (the 6 least significant bits

only) is incremented. The transfer is terminated by

the master generating a STOP condition.

When the master generates a STOP condition im-

mediately after the Ack bit (in the “10

th

bit” time

slot), either at the end of a byte write or a page

write, the internal memory write cycle is triggered.

A STOP condition at any other time does not trig-

ger the internal write cycle.

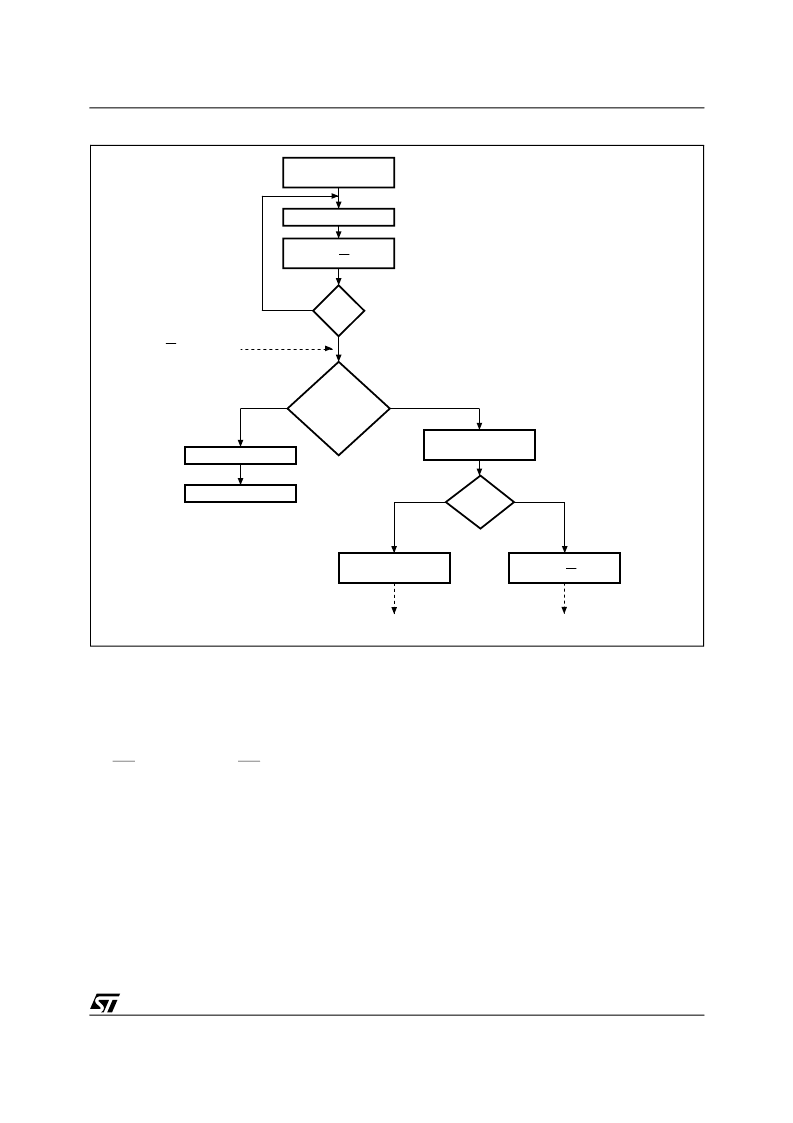

Figure 7. Write Cycle Polling Flowchart using ACK

WRITE Cycle

in Progress

AI01847C

Next

Operation is

Addressing the

Memory

START Condition

DEVICE SELECT

with RW = 0

ACK

Returned

YES

NO

YES

NO

ReSTART

STOP

DATA for the

WRITE Operation

DEVICE SELECT

with RW = 1

Send Address

and Receive ACK

First byte of instruction

with RW = 0 already

decoded by the device

YES

NO

START

Condition

Continue the

WRITE Operation

Continue the

Random READ Operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24128-MN5T | 256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| M24128-BN6T | 256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| M24128-BN5T | 256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| M24164 | 16 Kbit Serial I2C BUS EEPROM |

| M24164-R | 16 Kbit Serial I2C BUS EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24128-MW5T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| M24128-MW6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

| M24128S-FCU6T/T | 功能描述:IC EEPROM 128KBIT CSP 制造商:stmicroelectronics 系列:- 包裝:剪切帶(CT) 零件狀態(tài):有效 格式 - 存儲(chǔ)器:EEPROMs - 串行 存儲(chǔ)器類型:EEPROM 存儲(chǔ)容量:128K(16K x 8) 速度:400kHz 接口:I2C,2 線串口 電壓 - 電源:1.7 V ~ 5.5 V 工作溫度:-40°C ~ 85°C(TA) 封裝/外殼:4-XFBGA,WLCSP 供應(yīng)商器件封裝:4-WLCSP 標(biāo)準(zhǔn)包裝:1 |

| M24128T-FCU6T/TF | 功能描述:MEMORY 制造商:stmicroelectronics 系列:- 包裝:剪切帶(CT) 零件狀態(tài):有效 格式 - 存儲(chǔ)器:EEPROMs - 串行 存儲(chǔ)器類型:EEPROM 存儲(chǔ)容量:128K(16K x 8) 速度:400kHz 接口:I2C,2 線串口 電壓 - 電源:1.7 V ~ 5.5 V 工作溫度:-40°C ~ 85°C(TA) 封裝/外殼:4-XFBGA,WLCSP 供應(yīng)商器件封裝:4-WLCSP(0.83x0.83) 標(biāo)準(zhǔn)包裝:1 |

| M24128-WBN5T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/128 Kbit Serial IC Bus EEPROM Without Chip Enable Lines |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。