第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)

ES MT

M13S128168A

Elite Semiconductor Memory Technology Inc.

Publication Date : Jun. 2007

Revision : 1.8 20/49

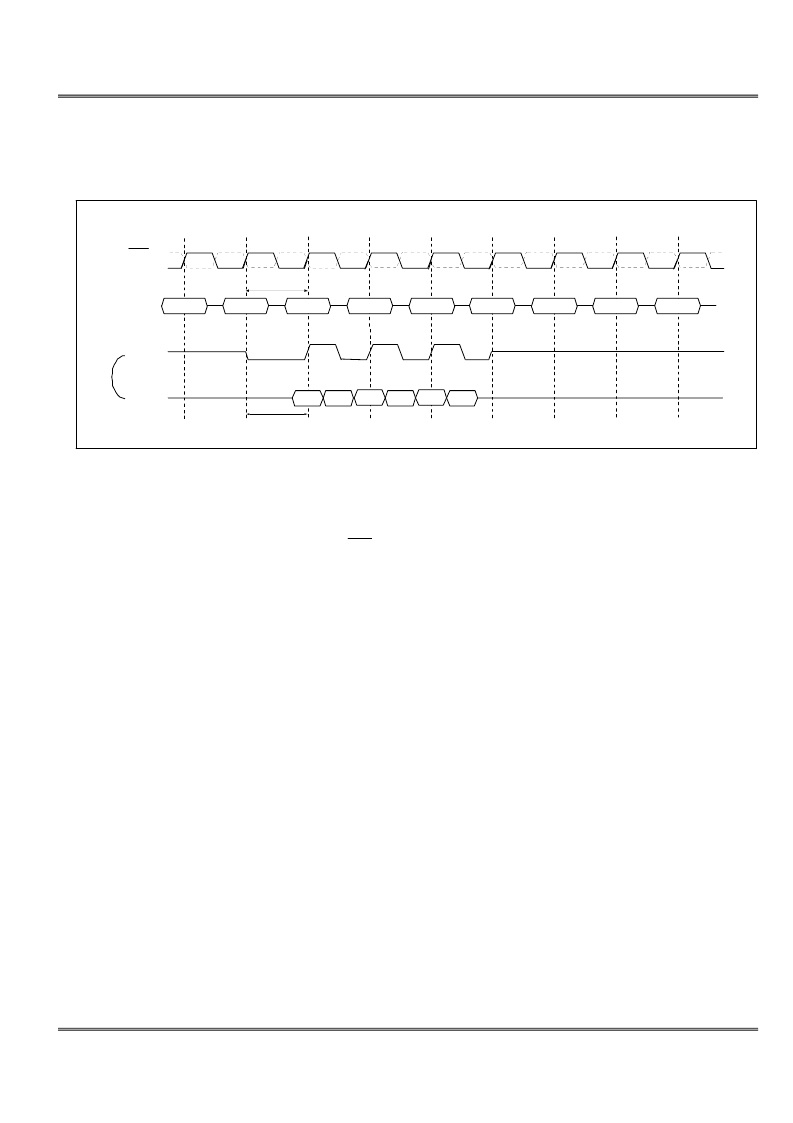

Write Interrupted by a Write

A Burst Write can be interrupted before completion of the burst by a new Write command, with the only restriction that the

interval that separates the commands must be at least one clock cycle. When the previous burst is interrupted, the remaining

addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

<Burst Length = 4>

The following functionality establishes how a Write command may interrupt a Read burst.

1. For Write commands interrupting a Read burst, a Read burst, a Burst Terminate command is required to stop the read burst

and tristate the DQ bus prior to valid input write data. Once the Burst Terminate command has been issued, the minimum

delay to a Write command = RU(CL) [CL is the CAS Latency and RU means round up to the nearest integer].

2. It is illegal for a Write command to interrupt a Read with autoprecharge command.

0

1

2

3

4

5

6

7

8

COMMAND

DQS

DQ's

NOP

NO P

NOP

NO P

NOP

NOP

Din A

0

WRITE A

Din A

1

Din B

0

Din B

1

Din B

2

Din B

3

1t

C K

NOP

WRITE B

CLK

CL K

t

C C D

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S128168A-5TG | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6BG | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6T | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6TG | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-7.5AB | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S128168A-5TG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-5TIG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6BG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6BIG | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6T | 制造商:ESMT 制造商全稱(chēng):Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。