- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9880HC Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | LXT9880HC |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 89/96頁 |

| 文件大?。?/td> | 1309K |

| 代理商: | LXT9880HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁當(dāng)前第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

LXT980/980A Dual-Speed, 5-Port Fast Ethernet Repeater

Datasheet

89

5.4.1

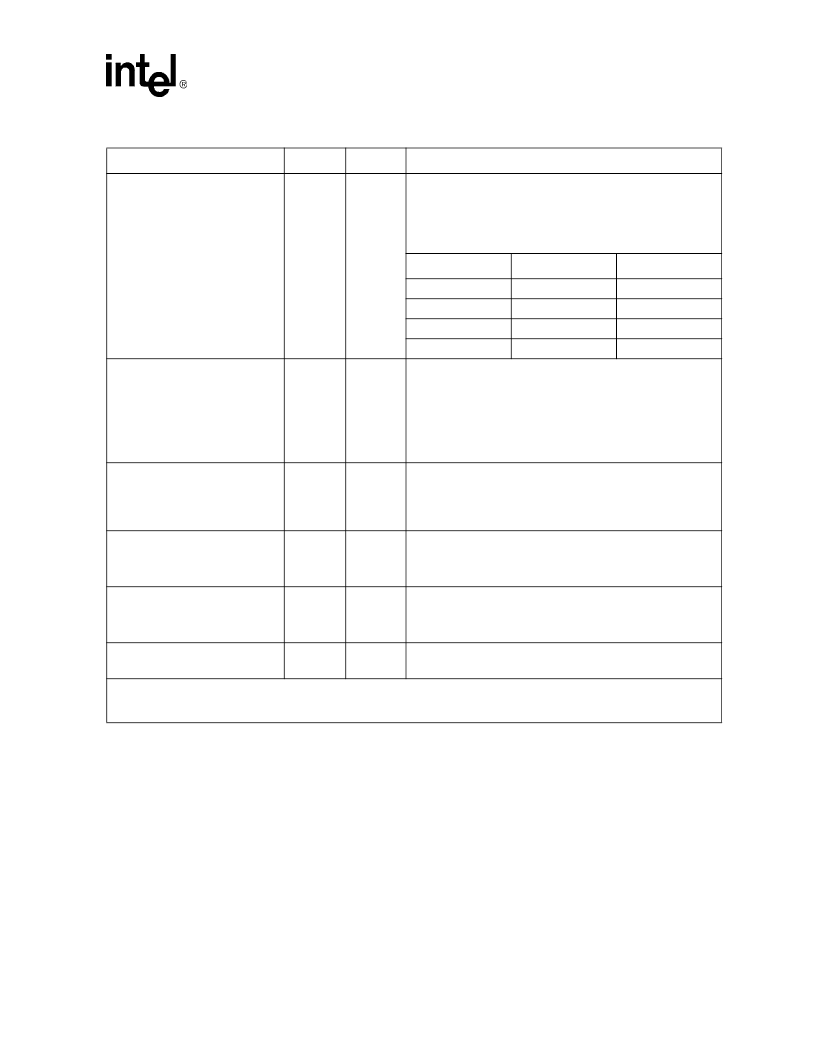

Repeater Configuration Register

This register contains many of the global repeater settings. The Repeater Configuration Register is

described in

Table 71

. Refer to

Table 70 on page 90

for bit assignments of the Repeater

Configuration Register.

Port LED Control Register

R/W

0B2

This register provides a measure of software control over the

port LEDs. Refer to

Table 74 on page 91

for bit assignments.

During reset, the state of this register is all 1s. If a manager is

present, this register remains in the all 1s state after reset.

Otherwise, the bits default to hardware control. Encoding is as

follows:

Bits 1 : 0

Modes 1 & 3

Mode 2

0 0

LED off

LED off

0 1

Reserved

LED fast blink

1 0

2

Hardware Control

Hardware Control

1 1

3

LED off

LED on steady

LED Timer Control Register

R/W

0B3

Refer to

Table 75 on page 91

for bit assignments. Bits 8-15 of

this register set the fast blink frequency of the LEDs. Bits 0-7 set

the slow blink frequency. The same formula is used in each case,

with a maximum of 128 Hz and a minimum of 0.5 Hz.

Example:

fast blink = x32 (0.4 sec)

slow blink = xCC (1.6 sec)

Repeater Reset Register

W

0B5

Writing any data value to this register with the Least Significant

Bit (LSB) = 1 causes the repeater functional logic to reset. (All

bits other than LSB do not matter.) The counters and

configuration information will be held static and will not be reset.

(default = 0s)

Software Reset Register

W

0B6

Writing any data value to this register with the Least Significant

Bit (LSB) = 1 is identical to a hardware reset. (All bits other than

LSB do not matter.) Everything is reset except the Source

Address RAM. (default = 0s)

Assign Address Register

(1 and 2)

W

188, 189

Refer to

Table 76 on page 91

for bit assignments. Writing a valid

48-bit ID (one that matches the EPROM ID) to this register

causes the device to change its Hub ID to the contents of the

EPROM ID register listed below. This register cannot be read.

EPROM Address Register

(1 and 2)

R

190, 191

These two registers contain the 48-bit ID read in from EPROM at

power-up. Refer to

Table 77 on page 91

for bit assignments.

Table 69. Configuration Registers (Continued)

Name

Type

1

Addr

Description

1. R = Read only; W = Write only; R/W = Read /Write.

2. Default value if manager is not present.

3. Default value if manager is present.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9883HC | LAN HUB CONTROLLER |

| LZ1030M | Common Anode Diode Array |

| LZ1032AD | Interface IC |

| LZ1032AM | Interface IC |

| LZ1032AR | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9883 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Umnmanaged Repeater |

| LXT9883HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN HUB CONTROLLER |

| LXTON/H0 | 制造商:Red Lion Controls 功能描述:ANNUN LABELS, 1 LPAX LABEL: TON/H 制造商:Red Lion Controls 功能描述:1 LPAX LABEL TON/H |

| LXTON000 | 制造商:Red Lion Controls 功能描述:ANNUNCIATOR LABELS,1 LPAX LABEL: TON 制造商:Red Lion Controls 功能描述:1 LPAX LABEL TON |

| LXU/MIN0 | 制造商:Red Lion Controls 功能描述:ANNUN LABELS, 1 LPAX LABEL: U/MIN 制造商:Red Lion Controls 功能描述:1 LPAX LABEL U/MIN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。