- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9782BC LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT9782BC |

| 英文描述: | LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|八路|的BGA | 272PIN |塑料 |

| 文件頁數(shù): | 60/68頁 |

| 文件大?。?/td> | 1177K |

| 代理商: | LXT9782BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當(dāng)前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

LXT9784

—

Low-Power Octal PHY

60

Datasheet

5.0

Register Definitions

The PHY registers can be accessed through the MII management interface.

Table 42

defines the bit type designations used in the following tables.

Table 42. Bit Type Designations

Designator

Definition

SC

Self Cleared

RO

Read Only

P

external Pin affects content

LL

Latch Low

LH

Latch High.

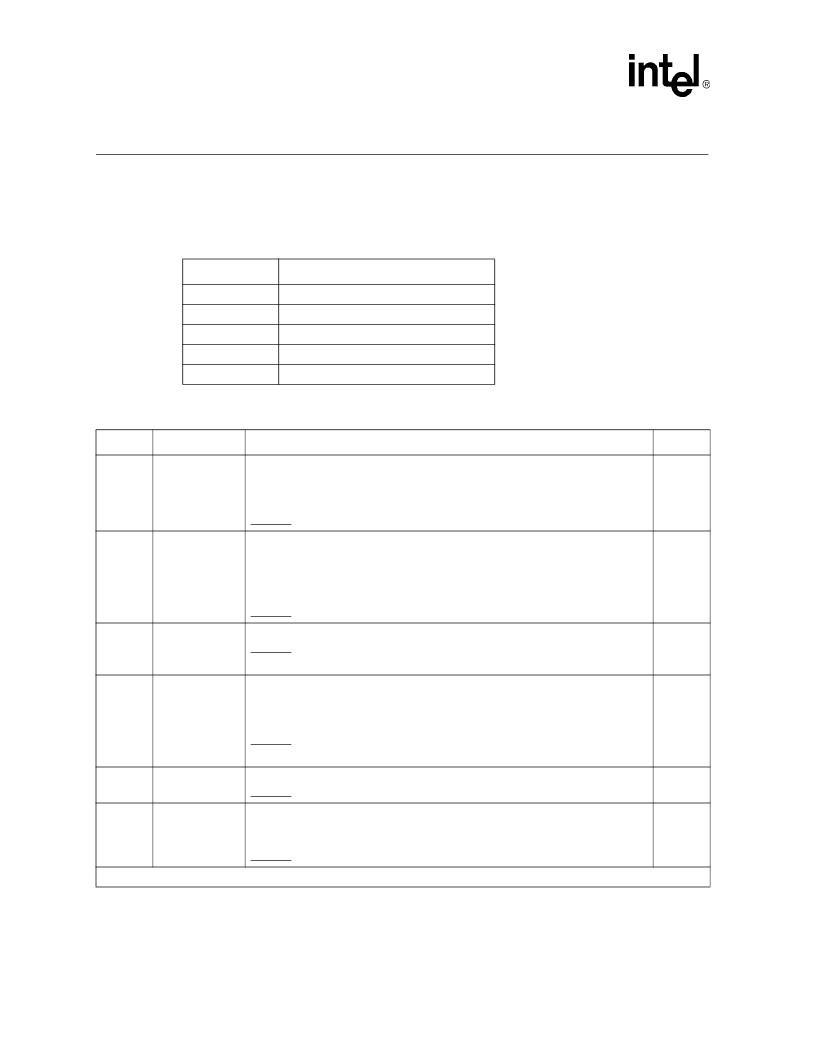

Table 43. Control Register (Register 0) Bit Definitions

Bit(s)

Name

Description

Type

1

0.15

Reset

Sets the status and control register of the PHY to their default states and is self-

clearing. The PHY returns a value of

“

1

”

when this register is read until the reset

process has completed and accepts a read or write transaction.

1 = PHY reset.

default 0 = normal operation.

RW

SC

0.14

Loopback

Enable loopback of transmit data to the receive data path. The PHY receive circuitry

is isolated from the network.

Note that this may cause the de-scrambler to lose synchronization and produce 560

ns of

“

dead time

”

.

1 = Loopback enabled.

default 0 = Loopback disabled (normal operation).

RW

0.13

Speed Selection

Controls speed when auto-negotiation is disabled.

default 1 = 100 MBPS

0 = 10 MBPS

RW

P

0.12

Auto-Negotiation

Enable

Bits 0.13 & 0.8 (Speed Selection and Duplex Mode, respectively) are ignored when

auto-negotiation is enabled.

Bits 4.12:5 (Technology Ability Field) depends on the PHY ability (Register 0) to

define the preferred link configuration.

default 1 = auto-negotiation enable.

0 = auto-negotiation disable.

RW

P

0.11

Power Down

1 = Analog section

only

power-down enabled.

default 0 = Power-down disabled (normal operation).

RW

0.10

Isolate

Allows the PHY to isolate the Media Independent Interface. The PHY doesn't

respond on the both transmit and receive activities.

1 = Logical isolate of internal MII interface.

default 0 = Normal operation.

RW

1. Refer to

Table 42

for Type definitions.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9782HC | LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| LXT980AHC | LAN HUB CONTROLLER |

| LXT980QC | LAN HUB CONTROLLER |

| LXT9860AHC | Controller Miscellaneous - Datasheet Reference |

| LXT9860HC | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9782HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| LXT9784 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Transceiver Hardware Integrity Function Overview |

| LXT9784BC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|BGA|324PIN|PLASTIC |

| LXT9784BE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|BGA|324PIN|PLASTIC |

| LXT9785 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。