- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9782BC LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT9782BC |

| 英文描述: | LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|八路|的BGA | 272PIN |塑料 |

| 文件頁數(shù): | 42/68頁 |

| 文件大?。?/td> | 1177K |

| 代理商: | LXT9782BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

LXT9784

—

Low-Power Octal PHY

42

Datasheet

2.9

Reset

When the LXT9784 RESET signal is asserted (active high) all internal circuits are reset. The PHY

can also be reset individually via the PHY register reset bit (register 0

’

h bit 15). Device clock

should be stable and running prior to HW RESET. Reset must be asserted for a minimum of 500

μ

s

for proper operation after de-assertion.

2.10

LED Operation

The LXT9784 has three pins per port dedicated to driving the LEDs. These drivers can indicate

link/activity, speed, and collision. The drivers also indicate that the PHY port was disabled by

management. The activity LED in this mode is triggered by both transmit and receive activities. All

three drivers are active Low.

The algorithm for computing media utilization is an average of the activity on the media over the

time of 8 maximum length packets, with minimum IPG spacing. The utilization is averaged over:

(8 packets * 1518 bytes * 8 bytes/bit * bit time) + (8 IPG * 96 bits * bit time)

The percent utilization is indicated by a specific frequency on the LED

n

_A (as shown in Table 17)

for a period of 600 ms (LED refresh rate), based on the activity of the prior 600 ms period.

In case the port is disabled, register 0.10 = 1, drivers LED

n

_A and LED

n

_B blink in unison, at a

rate of 1 Hz, 500 ms on and 500 ms off. Eliminate the indication of PHY port disable by setting the

PHY register 1B

’

h, bit 4. There is full controllability on all drivers through PHY register 1B

’

h, bits

[2:0].

The LED

n

_B state is frozen when a link is lost and is changed only after the link is re-established.

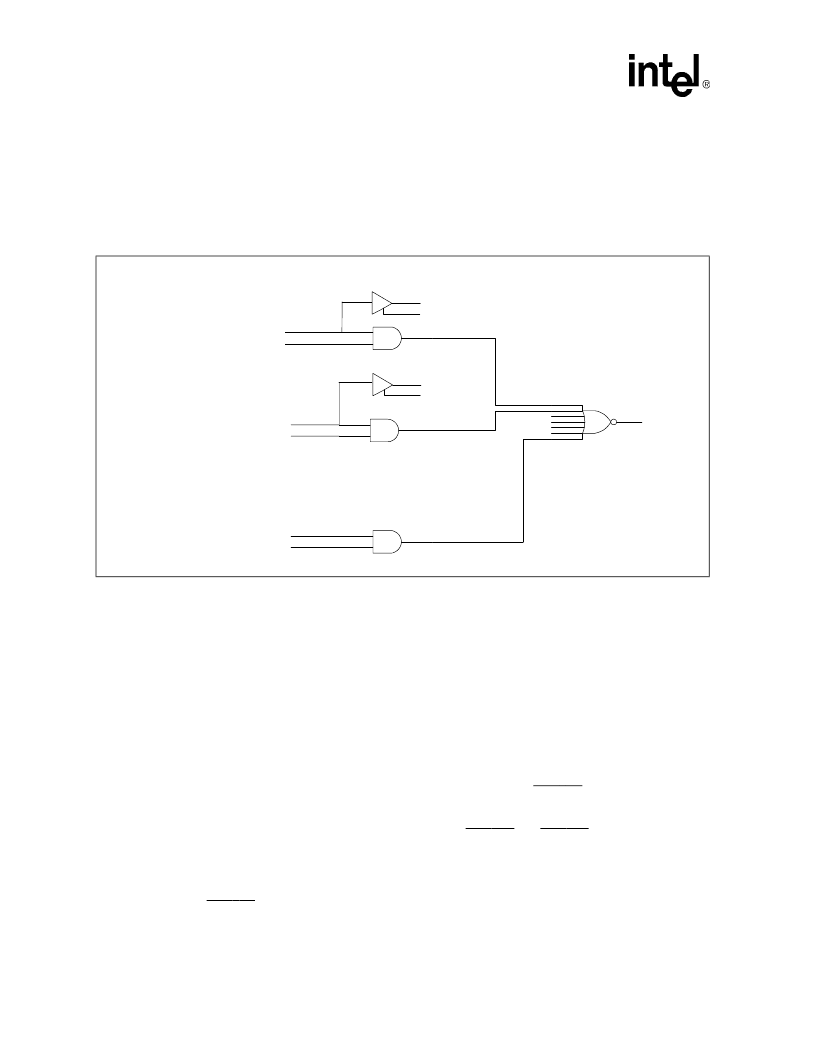

Figure 11. Simplified Interrupt Structure

Port 0 Status Changed = 1

Port Interrupt Enable from register 12

’

h

.

.

.

INT_L

Port 1 Status Changed = 1

Port Interrupt Enable from register 12

’

h

Port 7 Status Changed = 1

Port Interrupt Enable from register 12

’

h

Phy register 12

’

h bit 0

Read

Phy register 12

’

h bit 0

Read

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9782HC | LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| LXT980AHC | LAN HUB CONTROLLER |

| LXT980QC | LAN HUB CONTROLLER |

| LXT9860AHC | Controller Miscellaneous - Datasheet Reference |

| LXT9860HC | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9782HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| LXT9784 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Transceiver Hardware Integrity Function Overview |

| LXT9784BC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|BGA|324PIN|PLASTIC |

| LXT9784BE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN TRANSCEIVER|OCTAL|BGA|324PIN|PLASTIC |

| LXT9785 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。