- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369884 > LXT310PE PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT310PE |

| 英文描述: | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| 中文描述: | 的PCM收發(fā)器|單|的T 1(DS1的)|的CMOS | LDCC | 28腳|塑料 |

| 文件頁數(shù): | 7/26頁 |

| 文件大小: | 402K |

| 代理商: | LXT310PE |

T1 CSU/ISDN PRI Transceiver

—

LXT310

Datasheet

7

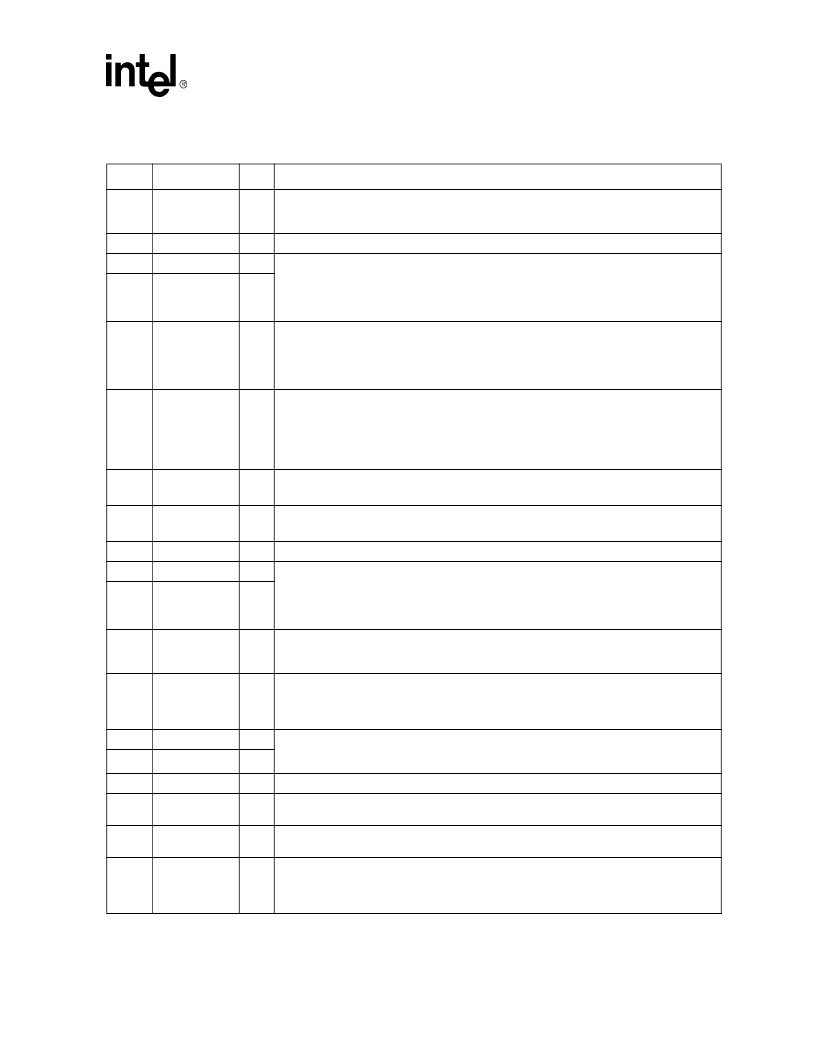

Table 1. Pin Descriptions

Pin #

Sym

I/O

Description

1

MCLK

I

Master Clock.

A 1.544 MHz clock input used to generate internal clocks. Upon Loss of

Signal (LOS), RCLK is derived from MCLK. If MCLK is not applied, this pin should be

grounded.

2

TCLK

I

Transmit Clock.

TPOS and TNEG are sampled on the falling edge of TCLK.

3

TPOS/TDATA

I

Transmit Data Input /Polarity Select.

Input data to be transmitted on the twisted-pair line.

Normally, pin 3 is TPOS and pin 4 is TNEG, the positive and negative sides of a bipolar input

pair. However, if pin 4 is held High for at least 16 TCLK cycles (equivalent to 15 successive

bipolar violations), the LXT310 switches to a unipolar I/O mode and transmit data is input on

pin 3. The LXT310 returns to bipolar I/O mode when pin 4 goes Low.

4

TNEG/UBS

I

5

MODE

I

Mode Select.

Setting MODE High selects the Host mode. In Host mode, the serial interface

is enabled for control and status reporting via a

μ

P. Setting MODE Low selects the Hardware

(H/W) mode. In Hardware mode the serial interface is disabled; hard-wired pins control

configuration and report status. Tying MODE to RCLK enables Hardware mode and the

B8ZS encoder/decoder.

6

7

RNEG

RPOS

(Bipolar I/O)

O

Receive Negative Data; Receive Positive Data.

In Bipolar Data I/O mode pins 6 and 7 are

bipolar data outputs. A signal on RNEG corresponds to detection of a negative pulse on

RTIP/RRING, and a signal on RPOS corresponds to a positive pulse on RTIP/RRING.

RNEG/RPOS outputs are Non Return-to-Zero (NRZ). In Host mode, CLKE determines the

clock edge at which these outputs are stable and valid. In Hardware mode both outputs are

stable and valid on the rising edge of RCLK.

6

BPV

(Unipolar I/O)

O

Bipolar Violation.

In Unipolar Data I/O mode, pin 6 goes High to indicate receipt of a Bipolar

Violation of the Alternate Mark Inversion (AMI) code.

7

RDATA

(Unipolar I/O)

O

Receive Data.

In Unipolar mode, data received from the twisted-pair line is output at pin 7.

8

RCLK

O

Recovered Clock.

This is the clock recovered from the signal received at RTIP and RRING.

9

XTALIN

I

Crystal Input; Crystal Output.

An external crystal (18.7 pF load capacitance, pullable)

operating at 6.176 MHz (four times the bit rate) is required to enable the jitter attenuation

function of the LXT310. These pins may also be used to disable the jitter attenuator by

connecting the XTALIN pin to the positive supply through a resistor, and leaving the

XTALOUT pin unconnected.

10

XTALOUT

O

11

JASEL

I

Jitter Attenuation Select.

Selects jitter attenuation location. When JASEL is High, the jitter

attenuator is active in the receive path. When JASEL is Low, the jitter attenuator is active in

the transmit path.

12

LOS

O

Loss of Signal.

LOS goes High when 175 consecutive spaces have been detected. LOS

returns Low when the received signal reaches a mark density of 12.5% (determined by

receipt of four marks within 32 bit periods). Received marks are output on RPOS and RNEG

even when LOS is High.

13

TTIP

O

Transmit Tip; Transmit Ring.

Differential Driver Outputs. These outputs are designed to

drive a 50 - 200

load. A transformer and line matching resistors can be selected to give the

desired pulse height.

16

TRING

O

14

TGND

–

Transmit Ground.

Ground return for the transmit drivers power supply TV+.

15

TV+

–

Transmit Power Supply.

+5 VDC power supply for the transmit drivers. TV+ must not vary

from RV+ by more than ±0.3 V.

17

EGL

I

Equalizer Gain Limit.

Sets equalizer gain. When EGL is Low, up to 36 dB of equalizer gain

may be added. When EGL is High, equalizer gain is limited to no more than 26 dB.

18

LATN

O

Line Attenuation Indication (See

Figure 3

).

Encoded output. The LATN pulse width,

relative to RCLK, indicates receive equalizer gain setting (line insertion loss at 772 kHz) in

7.5 dB steps. When LATN outputs 1 RCLK pulse, the equalizer is set at 7.5 dB gain, 2 pulses

= 15 dB, 3 pulses = 22.5 dB and 4 pulses = 0 dB. LATN is valid on the rising edge of RCLK.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT312JE | PCM Repeater |

| LXT312NE | PCM REPEATER|T-1(DS1)|CMOS|DIP|16PIN|PLASTIC |

| LXT312PE | PCM REPEATER|T-1(DS1)|CMOS|LDCC|44PIN|PLASTIC |

| LXT313JE | PCM Repeater |

| LXT313NE | PCM Repeater |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT310PE-IJC8 | 制造商:LEVE ONE 功能描述:310PE-IJC8 |

| LXT310PE-IQC8 | 制造商:LEVEL ONE 功能描述:310PE-IQC8 |

| LXT312 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Low Power T1 PCM Repeaters/Transceivers |

| LXT312JE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Repeater |

| LXT312NE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM REPEATER|T-1(DS1)|CMOS|DIP|16PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。