- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄39411 > LTC2157CUP-14#TRPBF (LINEAR TECHNOLOGY CORP) 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 PDF資料下載

參數(shù)資料

| 型號: | LTC2157CUP-14#TRPBF |

| 廠商: | LINEAR TECHNOLOGY CORP |

| 元件分類: | ADC |

| 英文描述: | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

| 封裝: | 9 X 9 MM, LEAD FREE, PLASTIC, MO-220WNJR-5, QFN-64 |

| 文件頁數(shù): | 11/32頁 |

| 文件大?。?/td> | 647K |

| 代理商: | LTC2157CUP-14#TRPBF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

19

21576514f

LTC2157-14/

LTC2156-14/LTC2155-14

APPLICATIONS INFORMATION

Clock Duty Cycle Stabilizer

For good performance the encode signal should have a

50% (±5%) duty cycle. If the optional clock duty cycle

stabilizer circuit is enabled, the encode duty cycle can

vary from 30% to 70% and the duty cycle stabilizer will

maintain a constant 50% internal duty cycle. The duty cycle

stabilizer is enabled via SPI Register A2 (see Table 3) or

by CS in parallel programming mode.

For applications where the sample rate needs to be changed

quickly, the clock duty cycle stabilizer can be disabled. In

this cases care should be taken to make the clock a 50%

(± 5%) duty cycle.

DIGITAL OUTPUTS

The digital outputs are double data rate LVDS signals. Two

data bits are multiplexed and output on each differential

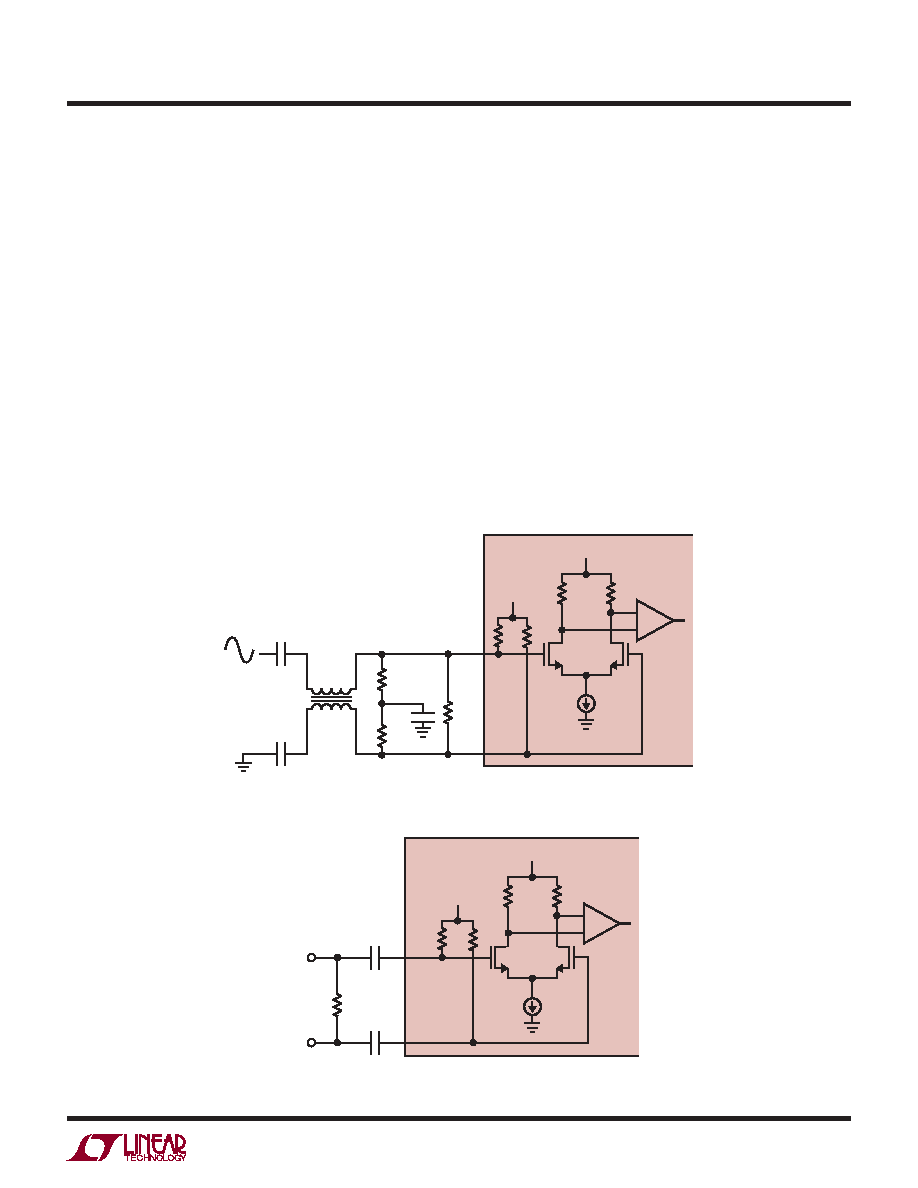

Figure 9. Sinusoidal Encode Drive

output pair. There are seven LVDS output pairs for chan-

nel A (DA0_1+/DA0_1– through DA12_13–/DA12_13+)

and seven pairs for channel B (DB0_1+/DB0_1– through

DB12_13–/DB12_13+). Overflow (OF+/OF–) and the data

output clock (CLKOUT+/CLKOUT–) each have an LVDS

output pair. Note that overflow for both channels is mul-

tiplexed onto the OF+/OF– output pair.

By default the outputs are standard LVDS levels: 3.5mA

output current and a 1.25V output common mode voltage.

Anexternal100Ωdifferentialterminationresistorisrequired

for each LVDS output pair. The termination resistors should

be located as close as possible to the LVDS receiver.

The outputs are powered by OVDD and OGND which are

isolated from the A/D core power and ground.

LTC2157-14

VDD

21576514 F09

1.2V

10k

50Ω

100Ω

50Ω

0.1μF

T1: MACOM

ETC1-1-13

Figure 10. PECL or LVDS Encode Drive

VDD

LTC2157-14

PECL OR

LVDS INPUT

21576514 F10

1.2V

10k

100Ω

0.1μF

ENC+

ENC–

相關PDF資料 |

PDF描述 |

|---|---|

| LTC2157IUP-14#PBF | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

| LTC2155IUP-14#TRPBF | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

| LTC2156IUP-14#PBF | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

| LTC2155CUP-14#PBF | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

| LTC2156CUP-14#TRPBF | 2-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC64 |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTC2157IUP-12#PBF | 制造商:Linear Technology 功能描述:ADC Dual Pipelined 250Msps 12-bit Parallel/Serial (SPI)/LVDS 64-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC DUAL 12BIT 250M 64-QFN |

| LTC2157IUP-12#TRPBF | 制造商:Linear Technology 功能描述:ADC Dual Pipelined 250Msps 12-bit Parallel/Serial (SPI)/LVDS 64-Pin QFN EP T/R 制造商:Linear Technology 功能描述:IC ADC DUAL 12BIT 250M 64-QFN |

| LTC2157IUP-14#PBF | 制造商:Linear Technology 功能描述:Dual ADC Pipelined 250Msps 14-bit Parallel/Serial (SPI)/LVDS 64-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC DUAL 250MSPS 64-QFN |

| LTC2157IUP-14#TRPBF | 制造商:Linear Technology 功能描述:IC ADC DUAL 250MSPS 64-QFN |

| LTC2158-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:30MHz to 1.4GHz IQ Demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復。