- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369841 > LSI53C895A LSI53C895A PCI to Ultra2 SCSI Controller technical manual v2.2 4/01 PDF資料下載

參數(shù)資料

| 型號(hào): | LSI53C895A |

| 英文描述: | LSI53C895A PCI to Ultra2 SCSI Controller technical manual v2.2 4/01 |

| 中文描述: | LSI53C895A PCI到Ultra2 SCSI控制器的技術(shù)手冊(cè)2.2版4 / 01 |

| 文件頁(yè)數(shù): | 87/166頁(yè) |

| 文件大小: | 1330K |

| 代理商: | LSI53C895A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)當(dāng)前第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)

SAF-TE Module

3-39

3.4.3 Interrupts

The LSI53C040 block diagram, Figure 2.1 in the

LSI53C040 Enclosure

Services Processor Technical Manual

, illustrates the primary elements of

the chip: 80C32 microcontroller, DMA core, SCSI core, 8067 core,

SRAM, dual TWS interfaces. In addition to these components, the

LSI53C040 contains several timer registers and access to multipurpose

I/O (MPIO) lines. The 80C32 microcontroller core has six interrupt

sources: Timer 0, Timer 1, Timer 2, Serial Port, External 0, and

External 1. These interrupt sources are controlled by writes to the

Special Function Registers (SFR). The latter two interrupt sources,

External 0 and External 1, provide the means by which interrupts from

the other elements in the LSI53C040 chip can be processed.

The LSI53C040 provides three registers to route interrupts to one of the

two external interrupts. A bit in the Interrupt Status Register (Program

Tag INT_STATUS, 0xFE04) will go high when an interrupt of the

appropriate type is pending. The Interrupt Mask Register (Program Tag

INT_MASK, 0xFE0D) can be used to prevent an interrupt from being

seen (and therefore processed) by the microcontroller core. The Interrupt

Destination Register (Program Tag INT_DESTINATION, 0xFE0E) can be

used to route any of the interrupts to External Interrupt 0 or External

Interrupt 1. The SAF-TE source code disables all interrupts except SCSI

and DMA, and routes these to External Interrupt 1 and 0 respectively. As

implemented, the 80C32 microcontroller processes the following

interrupts as shown in

Table 3.13

.

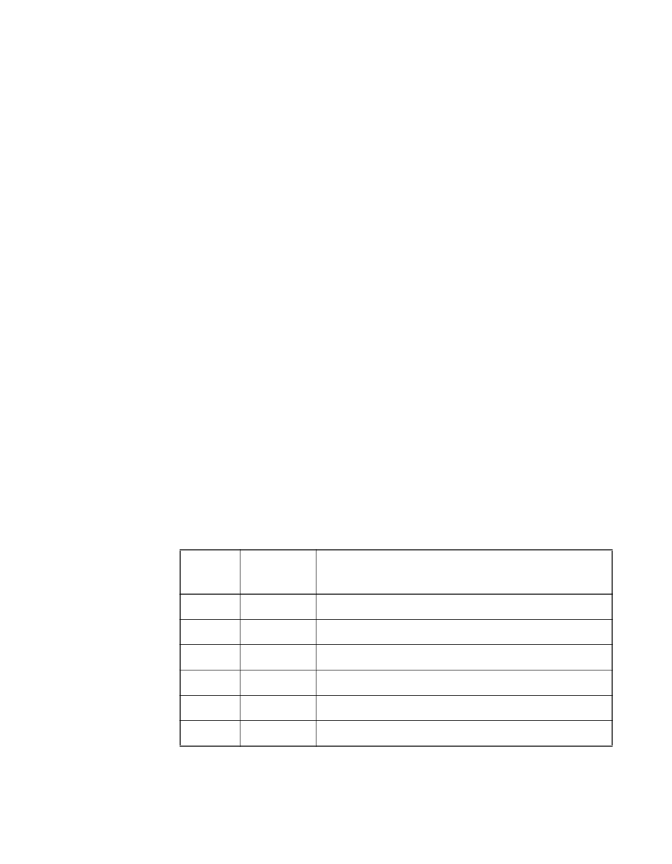

Table 3.13

Interrupts Processed by 80C32 Microcontroller

Interrupt

Pin

Vector

Address

safte.c

0

0x0003

External 0 (mapped to DMA Interrupts, if enabled)

1

0x000B

Timer 0 (SFRs 0x88–0x8A and 0x8C)

2

0x0013

External 1 (mapped to SCSI Interrupts)

3

0x001B

Timer 1 (SFR 0x88, 0x89, 0x8B, and 0x8D)

4

0x0023

Serial Port (SFR 0x98)

5

0x002B

Timer 2 (SFRs 0xC8, 0xCA–0xCD)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LSI53C896 | LSI53C896 PCI-dual channel Ultra2 SCSI multifunction controller |

| LSI53CF92A | LSI53CF92A Fast SCSI Controller technical manual v2.1 4/02 |

| LSI5464E | LSI5464E Ethernet host adapter |

| LSI60800 | LSI60800 PCI to USB host adapter user's guide v1.1 11/00? |

| LSI7000X | LSI7000X Fibre Channel:? single/dual & quad PCI-X host adapter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LSI53C895A-208QFP | 制造商:LSI Corporation 功能描述:Ultra SCSI Controller PCI/Flash Memory 208-Pin QFP |

| LSI53C895A208QFPLEADFREE | 制造商:LSI Corporation 功能描述: |

| LSI53C895A-272BGA LSA0564 | 制造商:LSI Corporation 功能描述: |

| LSI53C895A-272BGALEADFREE | 制造商:LSI Corporation 功能描述: |

| LSI53C896 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:ULTRA2 SCSI CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。