- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377664 > LS7366R (LSI Corporation) 32-BIT QUADRATURE COUNTER WITH SERIAL INTERFACE PDF資料下載

參數(shù)資料

| 型號: | LS7366R |

| 廠商: | LSI Corporation |

| 元件分類: | 通用總線功能 |

| 英文描述: | 32-BIT QUADRATURE COUNTER WITH SERIAL INTERFACE |

| 中文描述: | 32位正交計數(shù)器串行接口 |

| 文件頁數(shù): | 3/13頁 |

| 文件大?。?/td> | 101K |

| 代理商: | LS7366R |

STR.

The STR is an 8-bit status register which stores

count related status information.

7 6 5 4 3 2 1 0

CY BW CMP IDX CEN PLS U/D S

7366R-122205-3

IR

. The IR is an 8-bit register that fetches instruction bytes from

the received data stream and executes them to perform such

functions as setting up the operating mode for the chip (load the

MDR) and data transfer among the various registers.

B7 B6 B5 B4 B3 B2 B1 B0

B2 B1 B0 = XXX (Don’t care)

B5 B4 B3 = 000: Select none

= 001: Select MDR0

= 010: Select MDR1

= 011: Select DTR

= 100: Select CNTR

= 101: Select OTR

= 110: Select STR

= 111: Select none

B7 B6 = 00: CLR register

= 01: RD register

= 10: WR register

= 11: LOAD register

The actions of the four functions, CLR, RD, WR and LOAD are elaborated in Table 1.

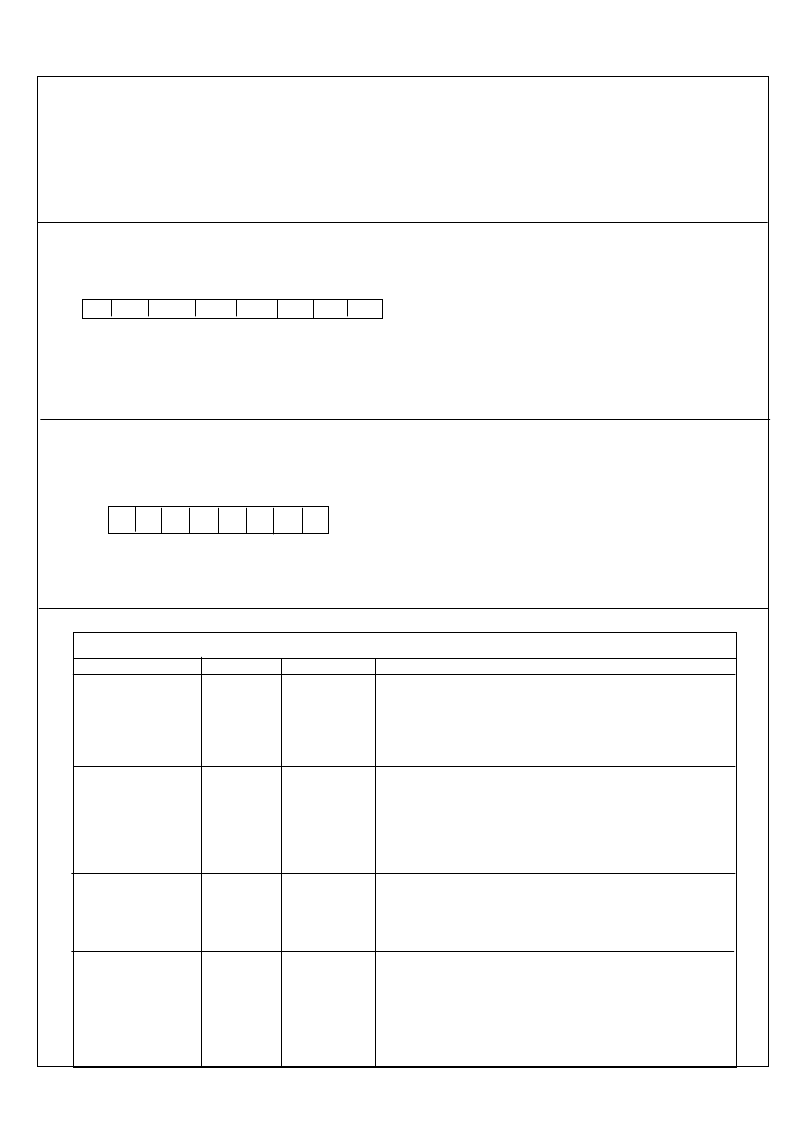

TABLE 1

Number of Bytes

OP Code Register

Operation

Clear MDR0 to zero

Clear MDR1 to zero

None

Clear CNTR to zero

None

Clear STR to zero

Output MDR0 serially on TXD (MISO)

Output MDR1 serially on TXD (MISO)

None

Transfer CNTR to OTR, then output OTR serially

on TXD (MISO)

Output OTR serially on TXD (MISO)

Output STR serially on TXD (MISO)

Write serial data at RXD (MOSI) into MDR0

Write serial data at RXD (MOSI) into MDR1

Write serial data at RXD (MOSI) into DTR

None

None

None

None

None

None

Transfer DTR to CNTR in “parallel”

Transfer CNTR to OTR in “parallel”

MDR0

MRD1

DTR

CNTR

OTR

STR

MDR0

MDR1

DTR

CNTR

1

CLR

2 to 5

RD

OTR

STR

MDR0

MDR1

DTR

CNTR

OTR

STR

MDR0

MDR1

DTR

CNTR

OTR

2 to 5

WR

1

LOAD

CNTR.

The CNTR is a software configurable 8, 16, 24 or 32-bit up/down counter which counts the up/down pulses resulting from

the quadrature clocks applied at the A and B inputs, or alternatively, in non-quadrature mode, pulses applied at the A input.

By means of IR intructions the CNTR can be cleared, loaded from the DTR or in turn, can be transferred into the OTR.

OTR.

The OTR is a software configuration 8, 16, 24 or 32-bit register which can be read back on the MISO output.

Since instantaneous CNTR value is often needed to be read while the CNTR continues to count, the OTR serves as a

convenient dump site for instantaneous CNTR data which can then be read without interfering with the counting process.

CY: Carry (CNTR overflow) latch

BW: Borrow (CNTR underflow) latch

CMP: Compare (CNTR = DTR) latch

IDX: Index latch

CEN: Count enable status: 0: counting disabled,

1: counting enabled

PLS: Power loss indicator latch; set upon power up

U/D: Count direction indicator: 0: count down, 1: count up

S: Sign bit. 1: negative, 0: positive

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LS7534 | DIMMER LIGHT SWITCH WITH UP AND DOWN CONTROLS |

| LS7535 | DIMMER LIGHT SWITCH WITH UP AND DOWN CONTROLS |

| LS7538 | TOUCH CONTROL STEP DIMMER LIGHT SWITCH WITH AUTOMATIC GAIN CONTROL (AGC) |

| LS7539 | TOUCH CONTROL STEP DIMMER LIGHT SWITCH WITH AUTOMATIC GAIN CONTROL (AGC) |

| LS7540 | TOUCH CONTROL CONTINUOUS DIMMER with AUTOMATIC GAIN CONTROL (AGC) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LS73-680-RM | 制造商:ICE 制造商全稱:ice Components, Ins. 功能描述:Surface Mount Power Inductors |

| LS73-681-RM | 制造商:ICE 制造商全稱:ice Components, Ins. 功能描述:Surface Mount Power Inductors |

| LS7-38-1 | 功能描述:電線鑒定 BLACK/WHITE 3/8" LAMINATED ADH. RoHS:否 制造商:TE Connectivity / Q-Cees 產(chǎn)品:Labels and Signs 類型: 材料:Vinyl 顏色:Blue 寬度:0.625 in 長度:1 in |

| LS7-38-2 | 功能描述:電線鑒定 BLACK/CLEAR 3/8" LAMINATED ADH. RoHS:否 制造商:TE Connectivity / Q-Cees 產(chǎn)品:Labels and Signs 類型: 材料:Vinyl 顏色:Blue 寬度:0.625 in 長度:1 in |

| LS73-820-RM | 制造商:ICE 制造商全稱:ice Components, Ins. 功能描述:Surface Mount Power Inductors |

發(fā)布緊急采購,3分鐘左右您將得到回復。