- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369786 > LM2618 PDF資料下載

參數(shù)資料

| 型號: | LM2618 |

| 文件頁數(shù): | 16/19頁 |

| 文件大小: | 2317K |

| 代理商: | LM2618 |

Application Information

(Continued)

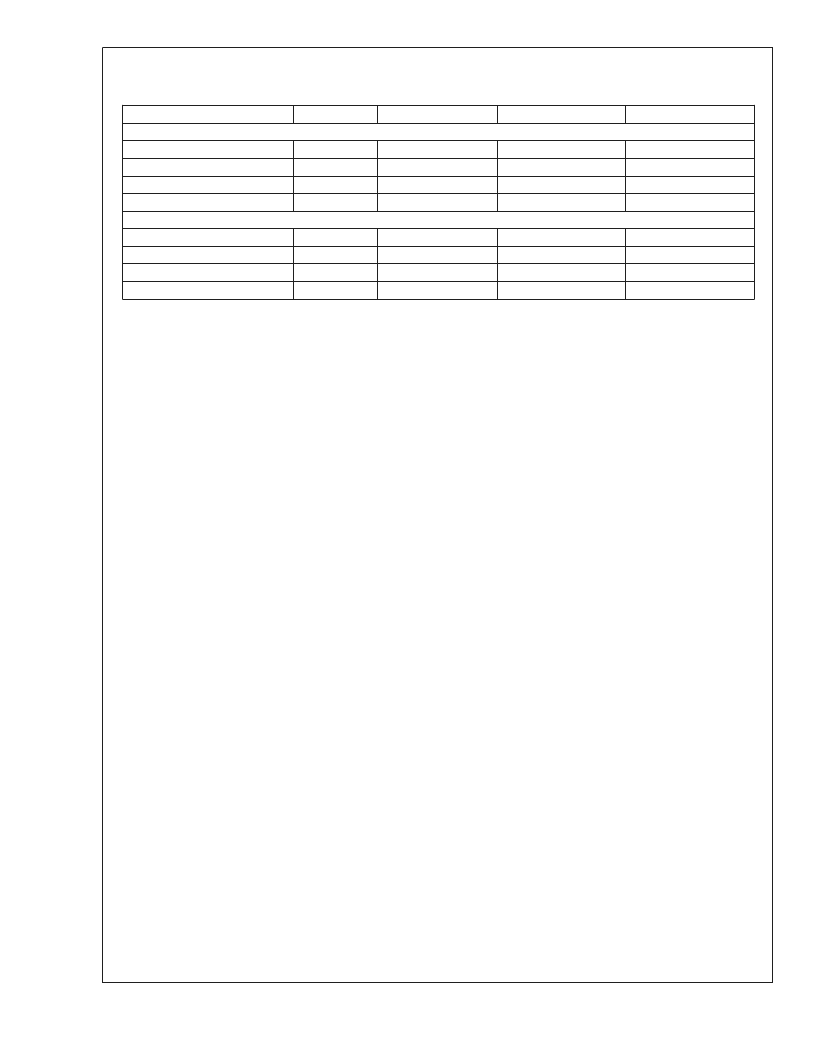

TABLE 3. Suggested Capacitors and Their Suppliers

Model

Size

Vendor

Phone

FAX

22μF, X7R or X5R Ceramic Capacitor for C2 (Output Filter Capacitor)

C3225X5RIA226M

1210

JMK325BJ226MM

1210

ECJ4YB0J226M

1210

GRM42-2X5R226K6.3

1210

10μF, 6.3V, X7R or X5R Ceramic Capacitor for C1 (Input Filter Capacitor)

C2012X5R0J106M

0805

JMK212BJ106MG

0805

ECJ3YB0J106K

1206

GRM40X5R106K6.3

0805

TDK

Taiyo-Yuden

Panasonic

muRata

847-803-6100

847-925-0888

714-373-7366

404-436-1300

847-803-6296

847-925-0899

714-373-7323

404-436-3030

TDK

Taiyo Yuden

Panasonic

muRata

847-803-6100

847-925-0888

714-373-7366

404-436-1400

847-803-6296

847-925-0899

714-373-7323

404-436-3030

Capacitor Selection

Use a 10μF, 6.3V, X7R or X5R ceramic input filter capacitor

and a 22uF, X7R or X5R ceramic output filter capacitor.

These provide an optimal balance between small size, cost,

reliability and performance. Do not use Y5V ceramic capaci-

tors.

Table 3

lists suggested capacitors and suppliers.

A 10μF ceramic capacitor can be used for the output filter

capacitor for smaller size in applications where the

worst-case transient load step is less than 200mA. Use of a

10μF output capacitor trades off smaller size for an increase

in output voltage ripple, and undershoot during line and load

transient response.

The input filter capacitor supplies current to the PFET switch

of the LM2612 in the first part of each cycle and reduces

voltage ripple imposed on the input power source. The out-

put filter capacitor smoothes out current flow from the induc-

tor to the load, helps maintain a steady output voltage during

transient load changes and reduces output voltage ripple.

These capacitors must be selected with sufficient capaci-

tance and sufficiently low ESR to perform these functions.

The ESR, or equivalent series resistance, of the filter capaci-

tors is a major factor in voltage ripple. The contribution from

ESR to voltage ripple is around 75-95% for most electrolytic

capacitors and considerably less for ceramic capacitors. The

remainder of the ripple is from charge storage due to capaci-

tance.

Diode Selection

An optional Schottky diode (D1 in Figure 1) can be added to

increase efficiency in PFM mode and PWM mode. This may

be desired in applications where increased efficiency for

improving operational battery life takes precedence over

increased system size associated with the Schottky diode.

Typically, use of an external schottky diode increases PFM

mode efficiency from 72.7% to 85.0% (20 mA load, V

=

1.8V, V

= 3.6V). See the efficiency curves in the

Typical

Operating Characteristics

.

Use a Schottky diode with a current rating higher than maxi-

mum current limit, such as an MBRM120T3 or MBRM140T3.

Use of a device rated for 30V or more reduces diode reverse

leakage in high temperature applications

Micro SMD Package Assembly and Use

Use of the micro SMD package requires specialized board

layout, precision mounting and careful reflow techniques, as

detailed

in

National

Semiconductor

AN-1112. Refer to the section

Surface Mount Technology

Application

Note

(SMT) Assembly Considerations

. For best results in assem-

bly, alignment ordinals on the PC board should be used to

facilitate placement of the device. Since micro SMD packag-

ing is a new technology, all layouts and assembly means

must be thoroughly tested prior to production. In particular,

proper placement, solder reflow and resistance to thermal

cycling must be verified.

The 10-Bump package used for the LM2612 has 300micron

solder balls and requires 10.82mil (0.275mm) pads for

mounting on the circuit board. The trace to each pad should

enter the pad with a 90 entry angle to prevent debris from

being caught in deep corners. Initially, the trace to each pad

should be 6 mil wide, for a section 6 mil long or longer, as a

thermal relief. Then each trace should neck up to its optimal

width over a span of 11 mils or more, so that the taper

extends beyond the edge of the package. The important

criterion is symmetry. This ensures the solder bumps on the

LM2612 re-flow evenly and that the device solders level to

the board. In particular, special attention must be paid to the

pads for bumps A3, B3, C3, D3 and A2. Because PVIN and

PGND are typically connected to large copper planes, inad-

equate thermal reliefs can result in late or inadequate reflow

of these bumps.

The pad style used with micro SMD package must be the

NSMD (non-solder mask defined) type. This means that the

solder-mask opening is larger than the pad size or 14.7mils

for the LM2612. This prevents a lip that otherwise forms if

the solder-mask and pad overlap. This lip can hold the

device off the surface of the board and interfere with mount-

ing. See Applications Note AN-1112 for specific instructions.

Board Layout Considerations

PC board layout is an important part of DC-DC converter

design. Poor board layout can disrupt the performance of a

DC-DC converter and surrounding circuitry by contributing to

EMI, ground bounce, and resistive voltage loss in the traces.

These can send erroneous signals to the DC-DC converter

IC, resulting in poor regulation or instability. Poor layout can

also result in reflow problems leading to poor solder joints

between the micro SMD package and board pads. Poor

solder joints can result in erratic or degraded performance.

Good layout for the LM2612 can be implemented by follow-

ing a few simple design rules:

L

www.national.com

16

相關PDF資料 |

PDF描述 |

|---|---|

| LM261J | Analog Comparator |

| LM2636M | Voltage-Mode SMPS Controller |

| LM2636MTC | Voltage-Mode SMPS Controller |

| LM2636MTCX | Voltage-Mode SMPS Controller |

| LM2636MX | Voltage-Mode SMPS Controller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LM2618ATL | 功能描述:IC REG BUCK SYNC ADJ 10-USMD RoHS:否 類別:集成電路 (IC) >> PMIC - 穩(wěn)壓器 - DC DC 開關穩(wěn)壓器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:降壓(降壓) 輸出類型:固定 輸出數(shù):1 輸出電壓:3.3V 輸入電壓:4.5 V ~ 24 V PWM 型:- 頻率 - 開關:- 電流 - 輸出:125mA 同步整流器:無 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 包裝:Digi-Reel® 供應商設備封裝:SOT-6 其它名稱:MAX1836EUT33#TG16DKR |

| LM2618ATLX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:400mA Sub-miniature, High Efficiency, Synchronous PWM & PFM Programmable DC-DC Converter |

| LM2618BTL | 功能描述:IC REG BUCK SYNC ADJ 10-USMD RoHS:否 類別:集成電路 (IC) >> PMIC - 穩(wěn)壓器 - DC DC 開關穩(wěn)壓器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:降壓(降壓) 輸出類型:固定 輸出數(shù):1 輸出電壓:3.3V 輸入電壓:4.5 V ~ 24 V PWM 型:- 頻率 - 開關:- 電流 - 輸出:125mA 同步整流器:無 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 包裝:Digi-Reel® 供應商設備封裝:SOT-6 其它名稱:MAX1836EUT33#TG16DKR |

| LM2618BTL/NOPB | 制造商:Texas Instruments 功能描述: |

| LM2618BTLX | 功能描述:IC REG BUCK SYNC ADJ 0.3A 10USMD RoHS:否 類別:集成電路 (IC) >> PMIC - 穩(wěn)壓器 - DC DC 開關穩(wěn)壓器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:降壓(降壓) 輸出類型:固定 輸出數(shù):1 輸出電壓:3.3V 輸入電壓:4.5 V ~ 24 V PWM 型:- 頻率 - 開關:- 電流 - 輸出:125mA 同步整流器:無 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 包裝:Digi-Reel® 供應商設備封裝:SOT-6 其它名稱:MAX1836EUT33#TG16DKR |

發(fā)布緊急采購,3分鐘左右您將得到回復。