- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358798 > LH543601P-35 (Sharp Corporation) 256 x 36 x 2 Bidirectional FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | LH543601P-35 |

| 廠商: | Sharp Corporation |

| 英文描述: | 256 x 36 x 2 Bidirectional FIFO |

| 中文描述: | 256 × 36 × 2雙向先進(jìn)先出 |

| 文件頁(yè)數(shù): | 9/43頁(yè) |

| 文件大小: | 360K |

| 代理商: | LH543601P-35 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

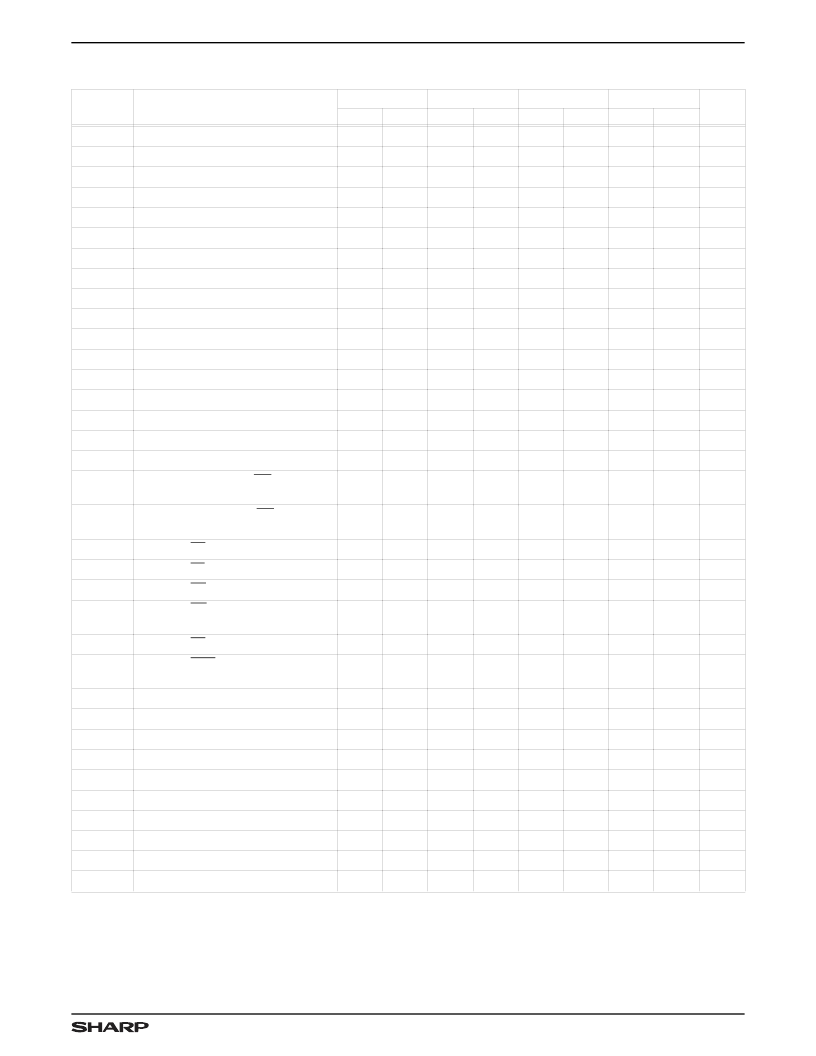

AC ELECTRICAL CHARACTERISTICS

1

(V

CC

= 5 V

±

10%, T

A

= 0

°

C to 70

°

C)

SYMBOL

DECRIPTION

–20

–25

–30

–35

UNITS

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

f

CC

t

CC

t

CH

t

CL

t

DS

t

DH

t

ES

t

EH

t

RWS

t

RWH

t

RQS

t

RQH

t

AS

t

AH

t

A

t

ACK

t

OH

Clock Cycle Frequency

—

50

—

40

—

33

—

28.5

MHz

Clock Cycle Time

Clock HIGH Time

Clock LOW Time

20

8

8

—

—

—

25

10

10

—

—

—

30

12

12

—

—

—

35

15

15

—

—

—

ns

ns

ns

Data Setup Time

Data Hold Time

Enable Setup Time

10

0

—

—

12

0

—

—

13

0

—

—

15

0

—

—

ns

ns

10.4

0

10.4

—

—

—

13

0

13

—

—

—

15

0

15

—

—

—

15

0

18

—

—

—

ns

ns

ns

Enable Hold Time

Read/Write Setup Time

Read/Write Hold Time

Request Setup Time

Request Hold Time

Address Setup Time

6

Address Hold Time

6

Data Output Access Time

0

12

0

—

—

—

0

15

0

—

—

—

0

18

0

—

—

—

0

21

0

—

—

—

ns

ns

ns

12

0

—

—

—

12.8

15

0

—

—

—

16

18

0

—

—

—

20

21

0

—

—

—

25

ns

ns

ns

Acknowledge Access Time

Output Hold Time

Output Enable Time, OE LOW to D

0

– D

35

Low-Z

2

Output Disable Time, OE HIGH to

D

0

– D

35

High-Z

2

Clock to EF Flag Valid (Empty Flag)

—

2.0

12

—

—

2.0

15

—

—

2.0

20

—

—

2.0

25

—

ns

ns

t

ZX

1.5

—

2.0

—

3.0

—

3.0

—

ns

t

XZ

—

9

—

12

—

15

—

20

ns

t

EF

t

FF

t

HF

—

17.6

—

22

—

25

—

30

ns

Clock to FF Flag Valid (Full Flag)

Clock to HF Flag Valid (Half-Full)

Clock to AE Flag Valid (Almost-

Empty)

—

—

17.6

17.6

—

—

22

22

—

—

25

25

—

—

30

30

ns

ns

t

AE

—

16

—

20

—

25

—

30

ns

t

AF

Clock to AF Flag Valid (Almost-Full)

Clock to MBF Flag Valid (Mailbox

Flag)

—

16

—

20

—

25

—

30

ns

t

MBF

—

12

—

15

—

20

—

25

ns

t

PF

t

RS

t

RSS

t

RSH

t

RF

t

FRL

t

FWL

t

BS

t

BH

t

BA

Data to Parity Flag Valid

Reset/Retransmit Pulse Width

7

Reset/Retransmit Setup Time

3

Reset/Retransmit Hold Time

3

Reset LOW to Flag Valid

First Read Latency

4

First Write Latency

5

Bypass Data Setup

—

13.6

—

—

—

17

—

—

—

20

—

—

—

25

—

—

ns

ns

ns

32/20

16

40/25

20

52/30

25

65/35

30

8

—

—

28

10

—

—

35

15

—

—

40

20

—

—

45

ns

ns

20

20

12

—

—

—

25

25

15

—

—

—

30

30

18

—

—

—

35

35

21

—

—

—

ns

ns

ns

Bypass Data Hold

Bypass Data Access

3

—

—

18

5

—

—

20

5

—

—

25

5

—

—

30

ns

ns

NOTES:

1.

Timing measurements performed at ‘AC Test Condition’ levels.

2.

Values are guaranteed by design; not currently production tested.

3.

t

RSS

and/or t

RSH

need not be met unless a rising edge of CK

A

occurs while EN

A

is being asserted, or else a rising edge of CK

B

occurs while

EN

B

is being asserted.

4.

t

FRL

is the minimum first-write-to-first-read delay, following an empty condition, which is required to assure valid read data.

5.

t

FWL

is the minimum first-read-to-first-write delay, following a full condtion, which is required to assure successful writing of data.

256

×

36

×

2 Bidirectional FIFO

LH543601

9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH543611 | 512 x 36 x 2 / 1024 x 36 x 2 Synchronous Bidirectional FIFO |

| LH543620 | 1024 x 36 Synchronous FIFO |

| LH5464-NR | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-Q | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-P | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH543611 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:512 x 36 x 2 / 1024 x 36 x 2 Synchronous Bidirectional FIFO |

| LH543611M-18 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous Bidirectional FIFO |

| LH543611M-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous Bidirectional FIFO |

| LH543611M-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous Bidirectional FIFO |

| LH543611M-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous Bidirectional FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。