- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377639 > LFX200C-3F900I (Lattice Semiconductor Corporation) The ispXPGA architecture PDF資料下載

參數(shù)資料

| 型號(hào): | LFX200C-3F900I |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | The ispXPGA architecture |

| 中文描述: | 在ispXPGA架構(gòu) |

| 文件頁(yè)數(shù): | 15/89頁(yè) |

| 文件大?。?/td> | 941K |

| 代理商: | LFX200C-3F900I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)

Lattice Semiconductor

ispXPGA Family Data Sheet

15

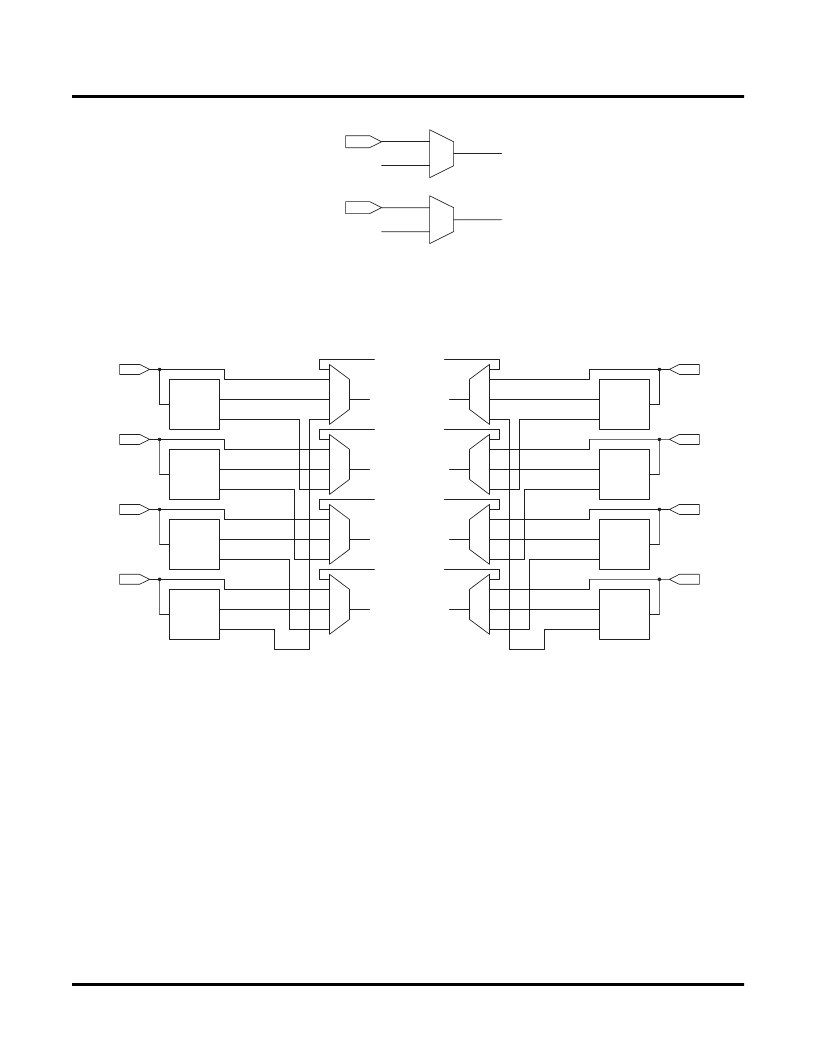

Figure 17. ispXPGA PLL_RST and PLL_FBK Generation

Clock Routing

The Global Clock Lines (GCLK) have two sources, their dedicated pins and the sysCLOCK circuit. Figure 18 illus-

trates the generation of the Global Clock Lines.

Figure 18. Global Clock Line Generation

sysIO Capability

All the ispXPGA devices have eight sysIO banks, where each bank is capable of supporting multiple I/O standards.

Each sysIO bank has its own I/O supply voltage (V

CCO

) and reference voltage (V

bank complete independence from the others. Each I/O is individually con

fi

gurable based on the bank’s V

V

REF

settings. In addition, each I/O has con

fi

gurable drive strength, weak pull-up, weak pull-down, or a bus-keeper

latch. Table 4 lists the number of I/Os supported per bank in each of the ispXPGA devices.

REF

) resources allowing each

CCO

and

Table 5 lists the sysIO standards with the typical values for V

CCO,

V

REF

and V

TT.

The TOE, JTAG TAP pins, PROGRAM, CFG0 and DONE pins of the ispXPGA device are the only pins that do not

have the sysIO capabilities. The TOE and CFG0 pins operate off the V

MOS standard corresponding to the device supply voltage. The TAP pins have a separate supply voltage (V

which determines the LVCMOS standard corresponding to that supply voltage.

CC

of the device, supporting only the LVC-

CCJ

),

There are three classes of I/O interface standards that are implemented in the ispXPGA devices. The

fi

rst is the un-

terminated, single-ended interface. It includes the 3.3V LVTTL standard along with the 1.8V, 2.5V, and 3.3V LVC-

MOS interface standards. Additionally, PCI and AGP-1X are subsets of this type of interface.

I/O/PLL_RST

I/O/PLL_FBK

From Routing

From Clock Net

To PLL

To PLL

PLL0

GCLK0

CLK_OUT0

SEC_OUT0

PLL1

CLK_OUT1

SEC_OUT1

GCLK1

PLL2

CLK_OUT2

SEC_OUT2

GCLK2

PLL3

CLK_OUT3

SEC_OUT3

GCLK3

PLL7

GCLK7

CLK_OUT7

SEC_OUT7

PLL6

CLK_OUT6

SEC_OUT6

GCLK6

PLL5

CLK_OUT5

SEC_OUT5

GCLK5

PLL4

CLK_OUT4

SEC_OUT4

GCLK4

CLK0

CLK1

CLK2

CLK3

CLK7

CLK6

CLK5

CLK4

From Routing

From Routing

From Routing

From Routing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFX500C-4F900I | The ispXPGA architecture |

| LFX1200C-03F900C | Circular Connector; MIL SPEC:MIL-C-26482, Series I; Body Material:Aluminum Alloy; Series:MS3112; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Solder; Circular Shell Style:Box Mount Receptacle RoHS Compliant: No |

| LFX1200C-03F900I | The ispXPGA architecture |

| LFX1200C-04F900C | The ispXPGA architecture |

| LFX500C-3F900C | Circular Connector; No. of Contacts:26; Series:; Body Material:Aluminum; Connecting Termination:Solder; Connector Shell Size:16; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:16-26 RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFX200C-3FE680C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX200C-3FE680I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX200C-3FH516C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX200C-3FH516I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX200C-3FN256C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。