- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377624 > LF2249 (Logic Devices Incorporated) 12 x 12-bit Digital Mixer PDF資料下載

參數(shù)資料

| 型號(hào): | LF2249 |

| 廠商: | Logic Devices Incorporated |

| 英文描述: | 12 x 12-bit Digital Mixer |

| 中文描述: | 12 × 12位數(shù)字調(diào)音臺(tái) |

| 文件頁數(shù): | 1/8頁 |

| 文件大?。?/td> | 70K |

| 代理商: | LF2249 |

DEVICES INCORPORATED

LF2249

12 x 12-bit Digital Mixer

12 x 12-bit Digital Mixer

Video Imaging Products

1

2

3

4

5

6

7

8

9

10

11

08/16/2000–LDS.2249-J

1

K

40 MHz Data and Computation Rate

K

Two 12 x 12-bit Multipliers with

Individual Data Inputs

K

Separate 16-bit Input Port for

Cascading Devices

K

Independent, User-Selectable 1–16

Clock Pipeline Delay for Each Data

Input

K

User-Selectable Rounding of Products

K

Fully Registered, Pipelined

Architecture

K

Three-State Outputs

K

Fully TTL Compatible

K

Replaces TRW/ Raytheon/ Fairchild

TMC2249

K

120-pin PQFP

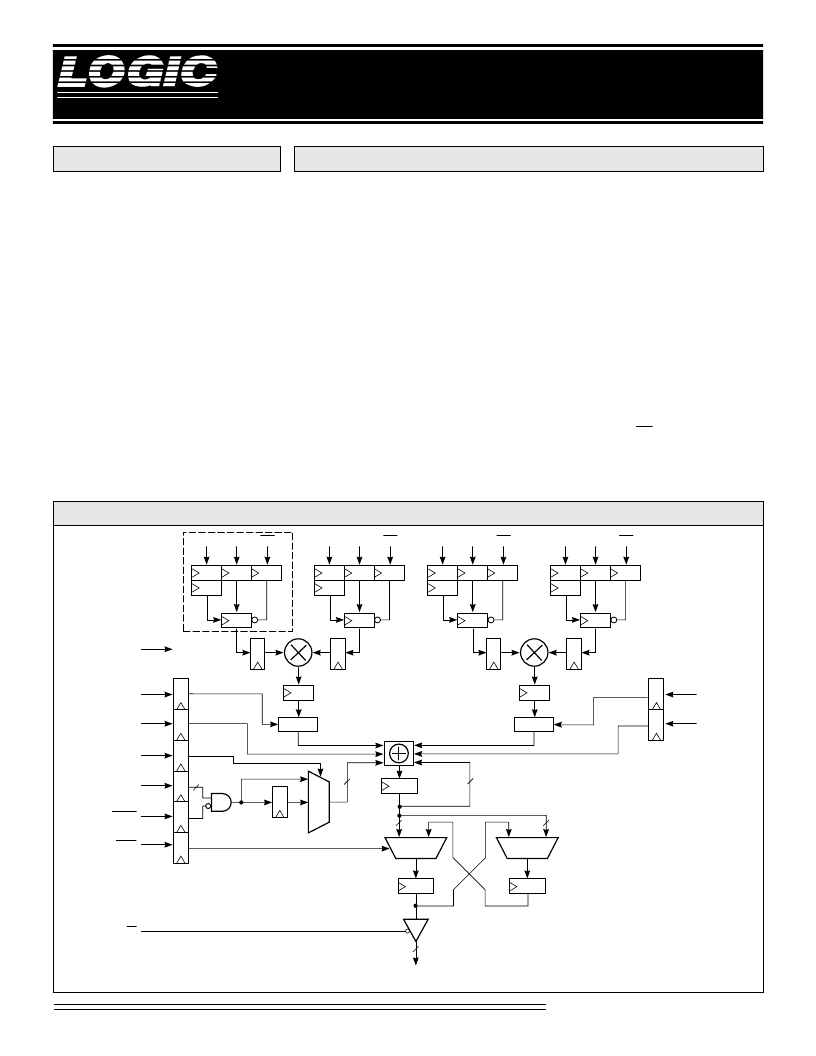

The

LF2249

is a high-speed digital

mixer comprised of two 12-bit

multipliers and a 24-bit accumulator.

All multiplier inputs are user acces-

sible, and each can be updated on

every clock cycle. The LF2249 utilizes

a pipelined architecture with fully

registered inputs and outputs and an

asynchronous three-state output

enable control for optimum flexibility.

Independent input register clock

enables allow the user to hold the

data inputs over multiple clock cycles.

Each multiplier input also includes a

user-selectable 1-16 clock pipeline

delay. The output of each multiplier

can be independently negated under

NEG

1

S

15-0

16

RND

FT

CAS

15-0

CASEN

SWAP

OE

4

4

3

2

24

16

2 : 1

2 : 1

16

2's COMP

1–16

1–16

ADEL

3-0

A

11-0

ENA

BDEL

3-0

B

11-0

ENB

2's COMP

1–16

1–16

CDEL

3-0

C

11-0

ENC

DDEL

3-0

D

11-0

END

4

4

NEG

2

ACC

CLK

NOTE: NUMBERS IN REGISTERS INDICATED

NUMBER OF PIPELINE DELAYS.

16

1

0

0

1

16

MS

LS

FEATURES

DESCRIPTION

user control for subtraction of prod-

ucts. The sum of the products can

also be internally rounded to 16 bits

during the accumulation process.

A separate 16-bit input port con-

nected to the accumulator is included

to allow cascading of multiple

LF2249s. Access to all 24 bits of the

accumulator is gained by switching

between upper or lower 16-bit words.

The accumulated output data is

updated on every clock cycle.

All inputs and outputs of the LF2249

are registered on the rising edge of

clock, except for OE. Internal pipeline

registers for all data and control

inputs are provided to maintain

DEVICES INCORPORATED

LF2249 B

LOCK

D

IAGRAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LF2272QC20 | Colorspace Converter/Corrector (3 x 12-bits) |

| LF2272QC25 | Colorspace Converter/Corrector (3 x 12-bits) |

| LF2272 | Colorspace Converter/Corrector (3 x 12-bits) |

| LF3304 | Dual Line Buffer/FIFO |

| LF3304QC10 | Circular Connector; No. of Contacts:23; Series:; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:16; Circular Contact Gender:Pin; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:16-99 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LF2249GC-25 | 制造商:LOGIC 功能描述: |

| LF2249GC-33 | 制造商:LOGIC 功能描述: |

| LF2249GC40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Mixer |

| LF2249GC-40 | 制造商:LOGIC 功能描述: |

| LF2249GM33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Mixer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。