- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358759 > LC72191M (Sanyo Electric Co.,Ltd.) PLL Frequency Synthesizer for Electronic Tuning in Car Stereo Tuners PDF資料下載

參數(shù)資料

| 型號: | LC72191M |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | PLL Frequency Synthesizer for Electronic Tuning in Car Stereo Tuners |

| 中文描述: | 鎖相環(huán)頻率合成調諧器在汽車音響電子調諧 |

| 文件頁數(shù): | 6/16頁 |

| 文件大?。?/td> | 194K |

| 代理商: | LC72191M |

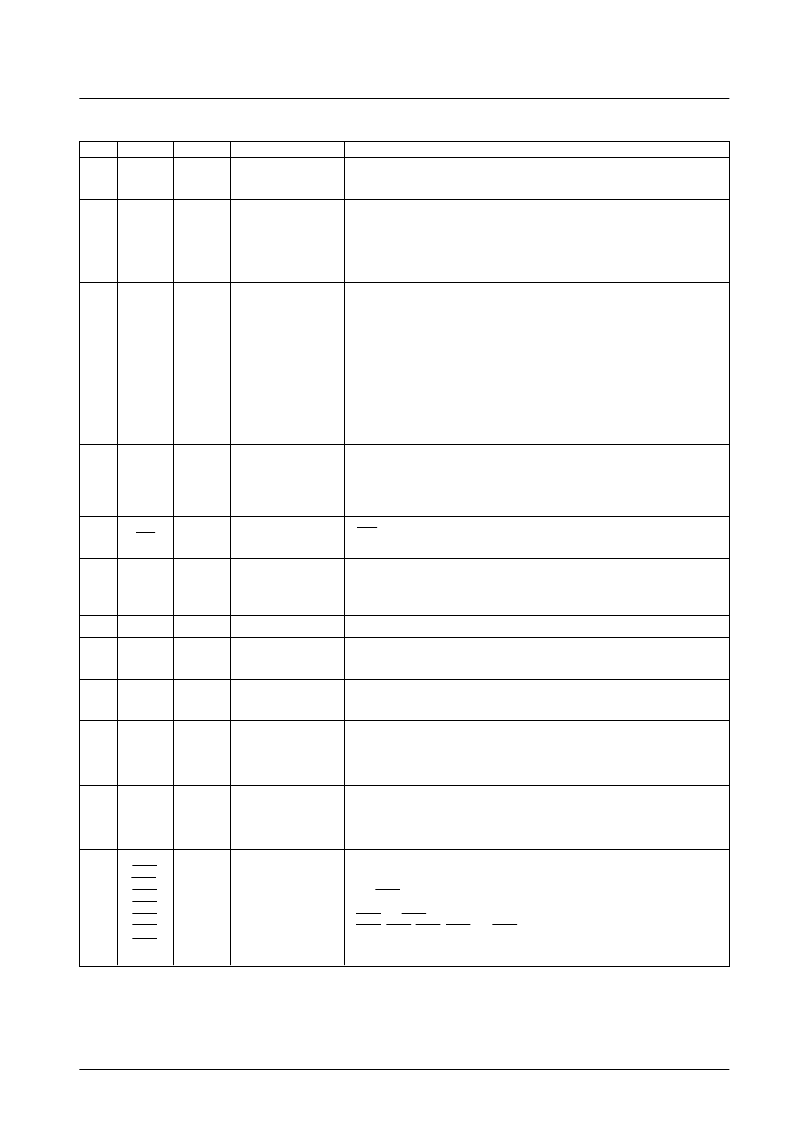

Pin Functions

Note:

*

1. The high and low level input voltages for the CE, CL, DI, IN0 and IN1 pins are V

IH

= 2.2 to 6.5 V and V

IL

= 0 to 0.7 V, regardless of the power

supply voltage V

DD

.

*

2. Since the output port states are undefined when power is first applied, transfer the control data quickly.

No. 3985-6/16

LC72191, 72191M, 72191JM

Pin No.

Symbol

I/O

Type

Function

1

24

19

18

21

22

6

20

23

2

4

3

5

X

IN

X

OUT

FMIN

AMIN

PD1

PD2

SYC

V

DD

V

SS

CE

CL

DI

DO

Input

Output

Input

Input

Three-state

N-channel

open drain

—

—

Input

*

1

Input

*

1

Input

*

1

Output

(N-channel

open drain)

Xtal OSC

Local oscillator signal

input

Local oscillator signal

input

Charge pump outputs

Controller clock

Power supply

Ground

Chip enable

Clock

Input data

Output data

Connections for a 7.2 MHz crystal oscillator

FMIN is selected when DV in the serial input data is set to 1.

Input frequency range: 10 to 130 MHz (70 mVrms minimum)

The signal passes through an internal divide-by-two prescaler and is then supplied to

the swallow counter.

Although the divisor setting is in the range 256 to 65,536, the actual divisor will be twice

the set value due to the presence of the internal divide-by-two prescaler.

AMIN is selected when DV in the serial input data is set to 0.

When SP in the serial input data is set to 1:

— Input frequency range: 2 to 40 MHz (70 mVrms minimum).

— The signal is supplied directly to the swallow counter without passing through the

internal divide-by-two prescaler.

— The divisor setting is in the range 256 to 65,536 and the actual divisor will be the

value set.

When SP in the serial input data is set to 0:

— Input frequency range: 0.5 to 10 MHz (70 mVrms minimum).

— The signal is supplied directly to a 12-bit programmable divider.

— The divisor setting is in the range 4 to 4,096 and the actual divisor will be the

value set.

PLL charge pump outputs. High levels are output from PD1 and PD2 when the local

oscillator frequency divided by n is higher than the reference frequency, and low levels

are output when that frequency is lower than the reference frequency.

These pins go to the floating state when the frequencies agree.

SYC is a controller clock source. The LC72191 outputs a 400 kHz 66% duty signal

from this pin after power is applied.

The LC72191 power supply pin. A voltage of between 4.5 and 6.5 V must be provided

when the PLL is operating. The supply voltage can be lowered to 3.5 V when only

operating the crystal oscillator circuit to acquire the controller clock and the clock time

base outputs.

The LC72191 ground pin

This pin must be set high when inputting serial data (via DI) or when outputting serial

data (via DO).

The clock input used for data signal synchronization during serial data input (via DI) or

output (via DO).

Input pin used when transferring serial data from the controller to the LC72191.

A total of 36 bits of data must be supplied to set up the LC72191 initial state.

Output pin used when transferring serial data to the controller from the LC72191.

A total of 28 bits from an internal shift register can be output in synchronization with the

CL signal.

Continued on next page.

9

10

11

12

13

14

17

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

Output

*

2

Output port

These pins latch bits O

0

to O

6

in the serial data transferred from the controller, invert

that data and output the inverted data in parallel.

The OUT0 pin can also be used to output an 8 Hz clock time base signal.

(When TB is 1.)

OUT1 and OUT2 are complementary outputs.

OUT0, OUT3, OUT4, OUT5 and OUT6 are N-channel open drain outputs that can

handle up to 13 V.

相關PDF資料 |

PDF描述 |

|---|---|

| LC7219 | PLL Frequency Synthesizers |

| LC7219M | PLL Frequency Synthesizers |

| LC7230-8221 | Single-chip PLL and Microcontroller with LCD Driver |

| LC7230-8272 | Single-chip PLL Controller |

| LC7232-8291 | 1-Chip PLL + Controller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LC72191M-TLM-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Tape and Reel |

| LC7219M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers |

| LC7220 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7221 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7222 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。