- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358759 > LC72134M (Sanyo Electric Co.,Ltd.) Dual PLL Frequency Synthesizer for FM Tuner Systems(用于FM調(diào)諧器的雙鎖相環(huán)頻率合成器) PDF資料下載

參數(shù)資料

| 型號(hào): | LC72134M |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | Dual PLL Frequency Synthesizer for FM Tuner Systems(用于FM調(diào)諧器的雙鎖相環(huán)頻率合成器) |

| 中文描述: | 雙鎖相環(huán)頻率合成調(diào)頻調(diào)諧器系統(tǒng)(用于調(diào)頻調(diào)諧器的雙鎖相環(huán)頻率合成器) |

| 文件頁(yè)數(shù): | 12/27頁(yè) |

| 文件大小: | 463K |

| 代理商: | LC72134M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

No.

Control block/data

Function

Related data

No. 5814-12/27

LC72134M

Continued from preceding page.

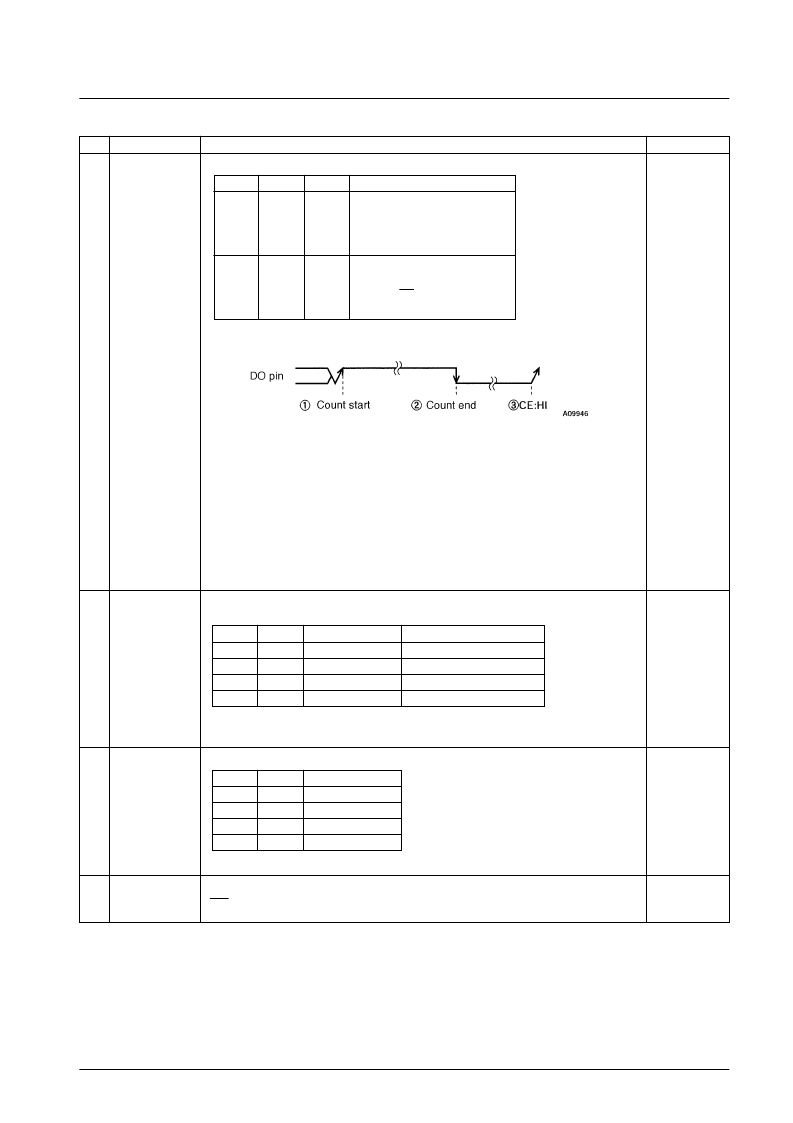

6

DO pin control data

DOC0

DOC1

DOC2

Determines the DO pin output.

The open state is selected after a power on reset.

*

1. end-UC: IF counter measurement end check

(1) When end-UC is selected and an IF count is started (by switching CTE from 0 to 1), the DO pin

automatically goes to the open state.

(2) When the IF counter measurement period completes, the DO pin goes to the low level, allowing

applications to test for the completion of the count period.

(3) The DO pin is set to the open state by performing a serial data input or output operation (when the

CE pin is set high).

*

2. Valid when the IFIN2/I1 pin is set to the input port state (L/I1 = 0).

(The DO pin will go to the open state if L/I1 is set to 1.)

*

3. Goes to the open state when the IO pin is set to the output state.

Note: During the data input period (the period that CE is high in IN1, IN2, or IN3 mode), the DO pin goes

to the open state regardless of the DO pin control data (DOC0 to DOC2). During the data output

period (the period that CE is high in OUT mode) the DO pin state reflects the internal DO serial

data in synchronization with the CL clock, regardless of the DO pin control data (DOC0 to DOC2).

UL0, UL1

ULa, ULb

CTE

L/I1

IOC2

7

Unlocked state

detection data

UL0, UL1

Selects the width of the phase error (E) detected for PLL lock state discrimination. A phase error is

recognized if a phase error in excess of the detection width occurs.

*

When the PLL is unlocked, the DO pin goes low and UL in the serial data output is set to 0.

When the PLL is locked, the DO pin goes high and UL in the serial data output is set to 1.

Dead zone width: DZA < DZB < DZC < DZD

DOC0

DOC1

DOC2

BO1

8

Phase comparator

control data

DZ0, DZ1

Controls the phase comparator dead zone

9

Clock time base

TBC

Setting the TBC bit to 1 causes an 8-Hz clock time base signal with a 40% duty to be output from the

BO1 pin. (The BO1 data will be ignored.)

DOC2

DOC1

DOC0

DO pin state

0

0

0

Open

0

0

1

Low when the PLL is unlocked

0

1

0

end-UC (See

*

1 below.)

0

1

1

Open

1

0

0

Open

1

0

1

IFIN2/I1 pin state (

*

2)

1

1

0

The IO2 pin state (

*

3)

1

1

1

Open

UL1

UL0

E detection width

Detection output

0

0

Stopped

Open

0

1

0

E is output directly

1

0

±0.55 μs

E is extended by 1 to 2 ms

1

1

±1.11 μs

E is extended by 1 to 2 ms

DZ1

DZ0

Dead band mode

0

0

DZA

0

1

DZB

1

0

DZC

1

1

DZD

Continued on next page.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72135M | PLL Frequency Synthesizer for Electronic Tuning(用于電子調(diào)諧的鎖相環(huán)頻率合成器) |

| LC72136N | PLL Frequency Synthesizer for Electronic Tuning(用于電子調(diào)諧的鎖相環(huán)頻率合成器) |

| LC72136 | PLL Frequency Synthesizer for Electronic Tuning(用于電子調(diào)諧的鎖相環(huán)頻率合成器) |

| LC72137 | PLL Frequency Synthesizer for Electronic Tuning(用于電子調(diào)諧的鎖相環(huán)頻率合成器) |

| LC72140 | PLL Frequency Synthesizer(鎖相環(huán)頻率合成器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72135M | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

| LC72135MA-AE | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| LC72135MA-Q-AE | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Tape and Reel 制造商:ON Semiconductor 功能描述:REEL / PLL FREQUENCY SYNTHESIZER |

| LC72135M-Q-TLM-E | 制造商:SANYO Semiconductor Co Ltd 功能描述: |

| LC72136 | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。