- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377611 > LC5256MC (Lattice Semiconductor Corporation) 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family PDF資料下載

參數(shù)資料

| 型號: | LC5256MC |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| 中文描述: | 3.3,2.5V和1.8V在系統(tǒng)可編程擴展可編程邏輯器件XPLD⑩家庭 |

| 文件頁數(shù): | 34/92頁 |

| 文件大?。?/td> | 378K |

| 代理商: | LC5256MC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

34

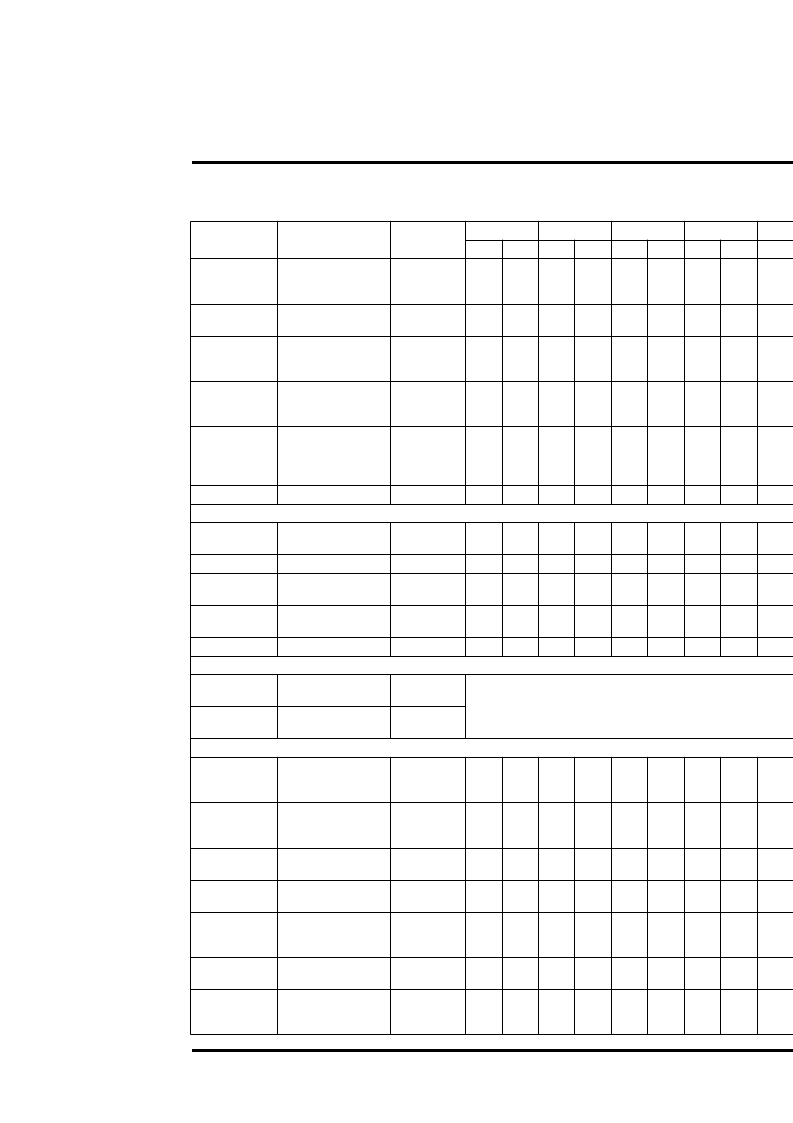

t

CASC

Additional Delay for

PT Cascading

between MFBs

Carry Chain Delay,

MFB to MFB

Carry Chain Delay,

Macro-Cell to

Macro-Cell

Routing Delay for

Extended Function

Flags

Additional Flag

Delay when

Expanding Data

Widths

Counter Sum Delay

—

—

0.71

—

0.80

—

0.89

—

0.92

—

1.33

ns

t

CICOMFB

—

—

0.35

—

0.39

—

0.44

—

0.46

—

0.66

ns

t

CICOMC

—

—

0.10

—

0.11

—

0.13

—

0.13

—

0.19

ns

t

FLAG

—

—

2.62

—

2.94

—

3.27

—

3.40

—

4.91

ns

t

FLAGEXP

t

FLAGFULL

,

t

FLAGAFULL,

t

FLAGEMPTY

,

t

FLAGAEMPTY

t

PTSA

—

2.57

—

2.89

—

3.21

—

3.34

—

4.82

ns

t

SUM

Optional Adjusters

—

0.80

—

0.90

—

1.00

—

1.04

—

1.50

ns

t

BLA

Block Loading

Adder

PT Expander Adder

Additional Delay for

the Input Register

Secondary PLL

Output Delay

MFB Input Extender

t

ROUTE

—

0.04

—

0.04

—

0.05

—

0.05

—

0.07

ns

t

EXP

t

ROUTE

—

0.53

—

0.60

—

0.66

—

0.69

—

0.99

ns

t

INDIO

t

INREG

—

0.50

—

0.56

—

0.63

—

0.65

—

0.94

ns

t

PLL_SEC_DELAY

t

PLL_DELAY

—

0.91

—

0.91

—

0.91

—

0.91

—

0.91

ns

t

INEXP

Input and Output Buffer Delays

Input Buffer Selec-

tion Adder

Output Buffer

Selection Adder

FIFO

Write Data Setup

before Write Clock

Time

Write Data Hold

after Write Clock

Time

Opposite Clock

Cycle Delay

Write Clock to Full

Flag Delay

Write Clock to

Almost Full Flag

Delay

Read Clock to

Empty Flag Delay

Read Clock to

Almost Empty Flag

Delay

t

ROUTE

—

0.62

—

0.70

—

0.78

—

0.81

—

1.16

ns

t

IOI

t

GCLK_IN,

t

IN,

t

GOE,

t

RST

Refer to sysIO Adjuster Tables

ns

t

IOO

t

BUF

t

FIFOWCLKS

—

-0.27

—

-0.27

—

-0.22

—

-0.22

—

-0.21

—

ns

t

FIFOWCLKH

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

ns

t

FIFOCLKSKEW

—

—

1.40

—

1.40

—

1.76

—

1.76

—

1.83

ns

t

FIFOFULL

—

—

3.08

—

3.08

—

3.85

—

3.85

—

4.00

ns

t

FIFOAFULL

—

—

3.08

—

3.08

—

3.86

—

3.86

—

4.01

ns

t

FIFOEMPTY

—

—

3.08

—

3.08

—

3.86

—

3.86

—

4.01

ns

t

FIFOAEMPTY

—

—

3.08

—

3.08

—

3.86

—

3.86

—

4.01

ns

ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

Over Recommended Operating Conditions

Parameter

Description

Base

Parameter

-4

-45

-5

-52

-75

Units

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC5256MC-4F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-5F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-75F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC5256MC-45F208C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-45F208I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-45F256C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-45F256I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5256MC-45F484C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。