- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377609 > LC4256V-5F256BC (LATTICE SEMICONDUCTOR CORP) 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs PDF資料下載

參數(shù)資料

| 型號: | LC4256V-5F256BC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| 中文描述: | EE PLD, 5 ns, PBGA256 |

| 封裝: | FPBGA-256 |

| 文件頁數(shù): | 34/74頁 |

| 文件大?。?/td> | 255K |

| 代理商: | LC4256V-5F256BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

Lattice Semiconductor

ispMACH 4000V/B/C/Z Family Data Sheet

34

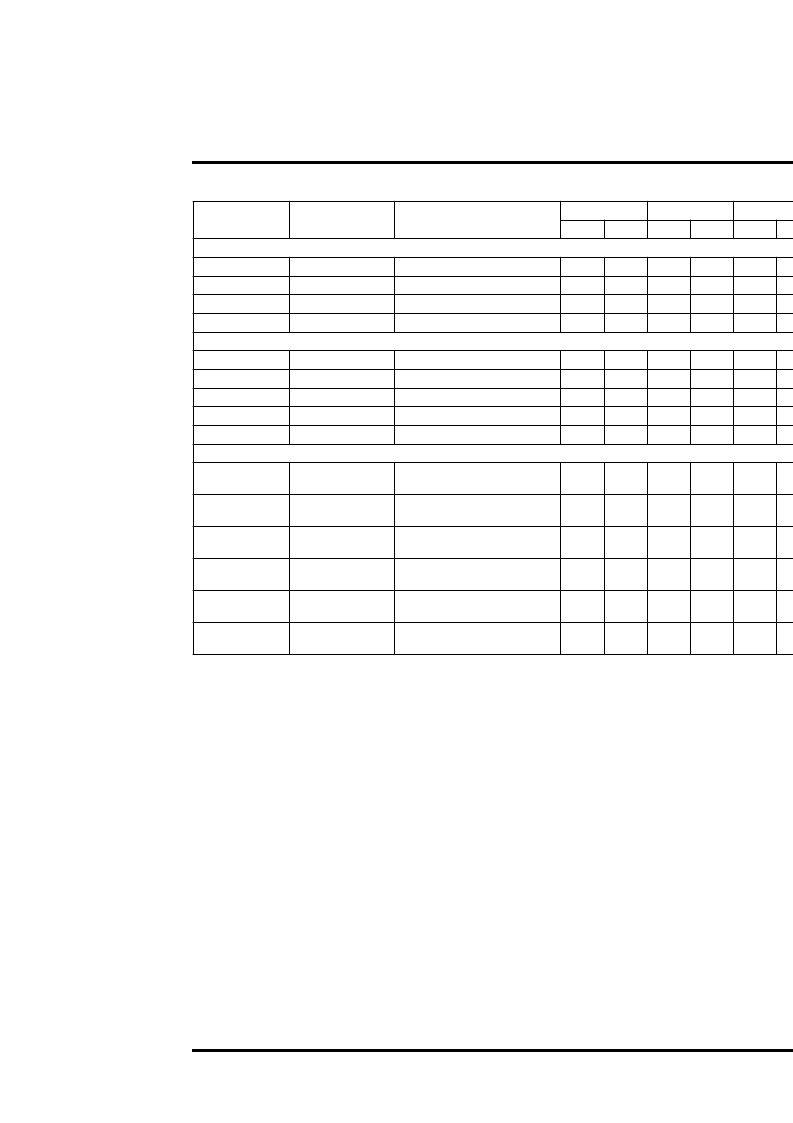

ispMACH 4032Z Timing Adders

1, 2

Adder

Type

Base

Parameter

Description

-35

-5

-7

Units

Min.

Max.

Min.

Max.

Min.

Max.

Optional Delay Adders

t

INDIO

t

EXP

t

ORP

t

BLA

t

IOI

Input Adjusters

LVTTL_in

LVCMOS33_in

LVCMOS25_in

LVCMOS18_in

PCI_in

t

IOO

Output Adjusters

LVTTL_out

t

INREG

t

MCELL

—

t

ROUTE

Input register delay

Product term expander delay

Output routing pool delay

Additional block loading adder

—

—

—

—

1.00

0.40

0.40

0.04

—

—

—

—

1.00

0.50

0.05

0.05

—

—

—

—

1.00

0.50

0.05

0.05

ns

ns

ns

ns

t

IN,

t

GCLK_IN,

t

GOE

t

IN,

t

GCLK_IN,

t

GOE

t

IN,

t

GCLK_IN,

t

GOE

t

IN,

t

GCLK_IN,

t

GOE

t

IN,

t

GCLK_IN,

t

GOE

Using LVTTL standard

Using LVCMOS 3.3 standard

Using LVCMOS 2.5 standard

Using LVCMOS 1.8 standard

Using PCI compatible input

—

—

—

—

—

0.70

0.70

0.40

0.00

0.70

—

—

—

—

—

0.70

0.70

0.40

0.00

0.70

—

—

—

—

—

0.70

0.70

0.40

0.00

0.70

ns

ns

ns

ns

ns

t

BUF,

t

EN,

t

DIS

Output con

fi

gured as TTL

buffer

Output con

fi

gured as 3.3V

buffer

Output con

fi

gured as 2.5V

buffer

Output con

fi

gured as 1.8V

buffer

Output con

fi

gured as PCI

compatible buffer

Output con

fi

gured for slow

slew rate

—

0.70

—

0.70

—

0.70

ns

LVCMOS33_out t

BUF,

t

EN,

t

DIS

—

0.70

—

0.70

—

0.70

ns

LVCMOS25_out t

BUF,

t

EN,

t

DIS

—

0.40

—

0.40

—

0.40

ns

LVCMOS18_out t

BUF,

t

EN,

t

DIS

—

0.00

—

0.00

—

0.00

ns

PCI_out

t

BUF,

t

EN,

t

DIS

—

0.70

—

0.70

—

0.70

ns

Slow Slew

t

BUF,

t

EN

—

1.00

—

1.00

—

1.00

ns

1. Preliminary information.

2. Refer to Technical Note TN 1004: ispMACH 4000 Timing Model Design and Usage Guidelines for information regarding use of these

adders.

Note: Open drain timing is the same as corresponding LVCMOS timing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC4256V-5F256BI | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-5T144C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-5T144I | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4032ZC-35M56C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| LC4000B | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC4256V-5F256BC1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-5F256BI | 功能描述:CPLD - 復雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4256V-5F256BI1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256V-5FN256AC | 功能描述:CPLD - 復雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4256V-5FN256AC1 | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

發(fā)布緊急采購,3分鐘左右您將得到回復。