- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377609 > LC4128C-27T128C (LATTICE SEMICONDUCTOR CORP) 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs PDF資料下載

參數(shù)資料

| 型號: | LC4128C-27T128C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| 中文描述: | EE PLD, 2.7 ns, PQFP128 |

| 封裝: | TQFP-128 |

| 文件頁數(shù): | 13/74頁 |

| 文件大?。?/td> | 255K |

| 代理商: | LC4128C-27T128C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

Lattice Semiconductor

ispMACH 4000V/B/C/Z Family Data Sheet

13

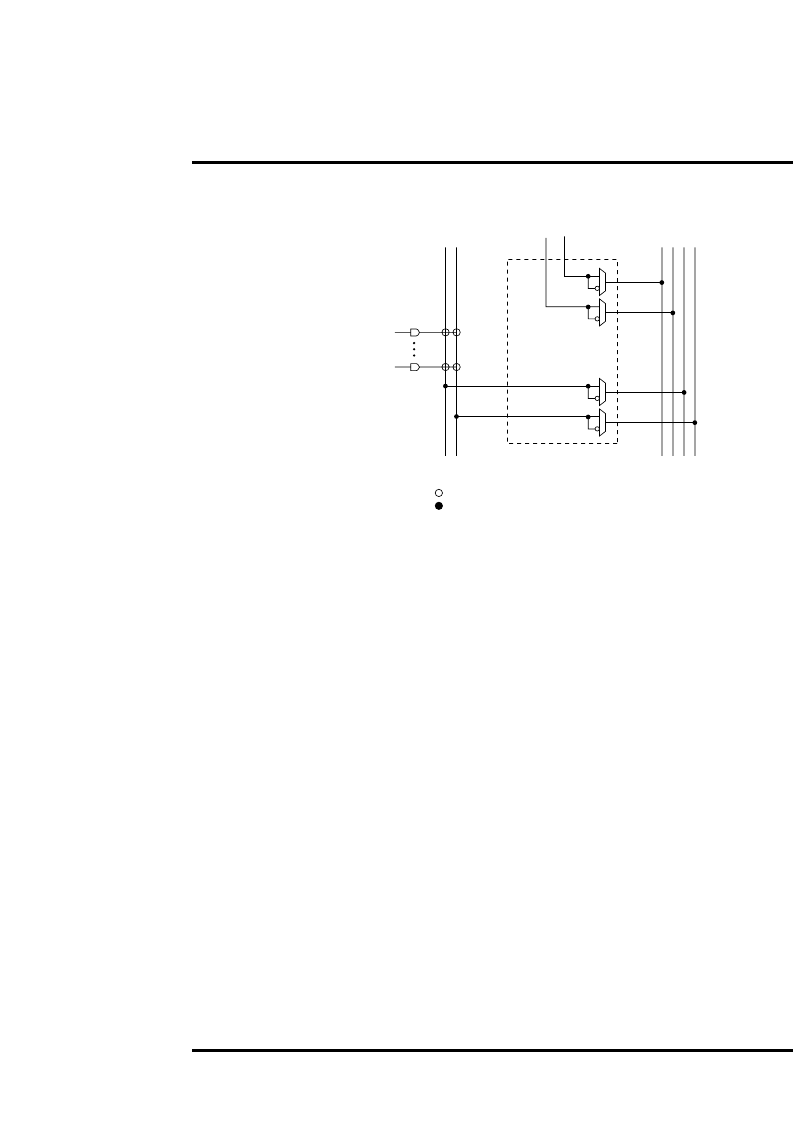

Figure 10. Global OE Generation for ispMACH 4032

Zero Power/Low Power and Power Management

The ispMACH 4000 family is designed with high speed low power design techniques to offer both high speed and

low power. With an advanced E

2

low power cell and non sense-ampli

fi

er design approach (full CMOS logic

approach), the ispMACH 4000 family offers SuperFAST pin-to-pin speeds, while simultaneously delivering low

standby power without needing any “turbo bits” or other power management schemes associated with a traditional

sense-ampli

fi

er approach.

The zero power ispMACH 4000Z is based on the 1.8V ispMACH 4000C family. With innovative circuit design

changes, the ispMACH 4000Z family is able to achieve the industry’s “l(fā)owest static power”.

IEEE 1149.1-Compliant Boundary Scan Testability

All ispMACH 4000 devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows

functional testing of the circuit board on which the device is mounted through a serial scan path that can access all

critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto

test nodes, or test node data to be captured and shifted out for veri

fi

cation. In addition, these devices can be linked

into a board-level serial scan path for more board-level testing. The test access port operates with an LVCMOS

interface that corresponds to the power supply voltage.

I/O Quick Con

fi

guration

To facilitate the most ef

fi

cient board test, the physical nature of the I/O cells must be set before running any continu-

ity tests. As these tests are fast, by nature, the overhead and time that is required for con

fi

guration of the I/Os’

physical nature should be minimal so that board test time is minimized. The ispMACH 4000 family of devices allows

this by offering the user the ability to quickly con

fi

gure the physical nature of the I/O cells. This quick con guration

takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's

ispVM System programming software can either perform the quick con

fi

guration through the PC parallel port, or

can generate the ATE or test vectors necessary for a third-party test system.

Shared PTOE

(Block 0)

Shared PTOE

(Block 1)

Global

Fuses

GOE (3:0)

to I/O cells

Internal Global OE

PT Bus

(2 lines)

4-Bit

Global OE Bus

Global OE

Fuse connection

Hard wired

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC4128V-10T144I | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4128V-27T100C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4128V-27T128C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4128V-27T144C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4128V-5T144C | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC4128C-27TN100C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4128C-27TN128C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4128C-5T100C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4128C-5T100I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC4128C-5T128C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。