- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358741 > LAN91C100FD (SMSC Corporation) FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY PDF資料下載

參數(shù)資料

| 型號(hào): | LAN91C100FD |

| 廠商: | SMSC Corporation |

| 英文描述: | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| 中文描述: | 宴快速以太網(wǎng)控制器以全雙工能力 |

| 文件頁(yè)數(shù): | 28/79頁(yè) |

| 文件大小: | 585K |

| 代理商: | LAN91C100FD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)

FEAST Fast Ethernet Controller with Full Duplex Capability

Rev.

10/14/2002

Page 28

SMSC DS – LAN91C100FD Rev. D

PRELIMINARY

NO WAIT - When set, does not request additional wait states. An exception to this are accesses to the

Data Register if not ready for a transfer. When clear, negates IOCHRDY for two to three clocks on any

cycle to the LAN91C100FD.

FULL STEP - This bit is a general purpose output port. Its inverse value drives pin nFSTEP and it is

typically connected to SEL pin of the LAN83C694. It can be used to select the signaling mode for the AUI

or as a general purpose non-volatile configuration pin. Defaults low.

AUI SELECT - This bit is a general purpose output port. Its value drives pin AUISEL and it is typically

connected to MODE1 pin of the LAN83C694. It can be used to select AUI vs. 10BASE-T, or as a general

purpose non-volatile configuration pin. Defaults low.

Reserved - Must be 0.

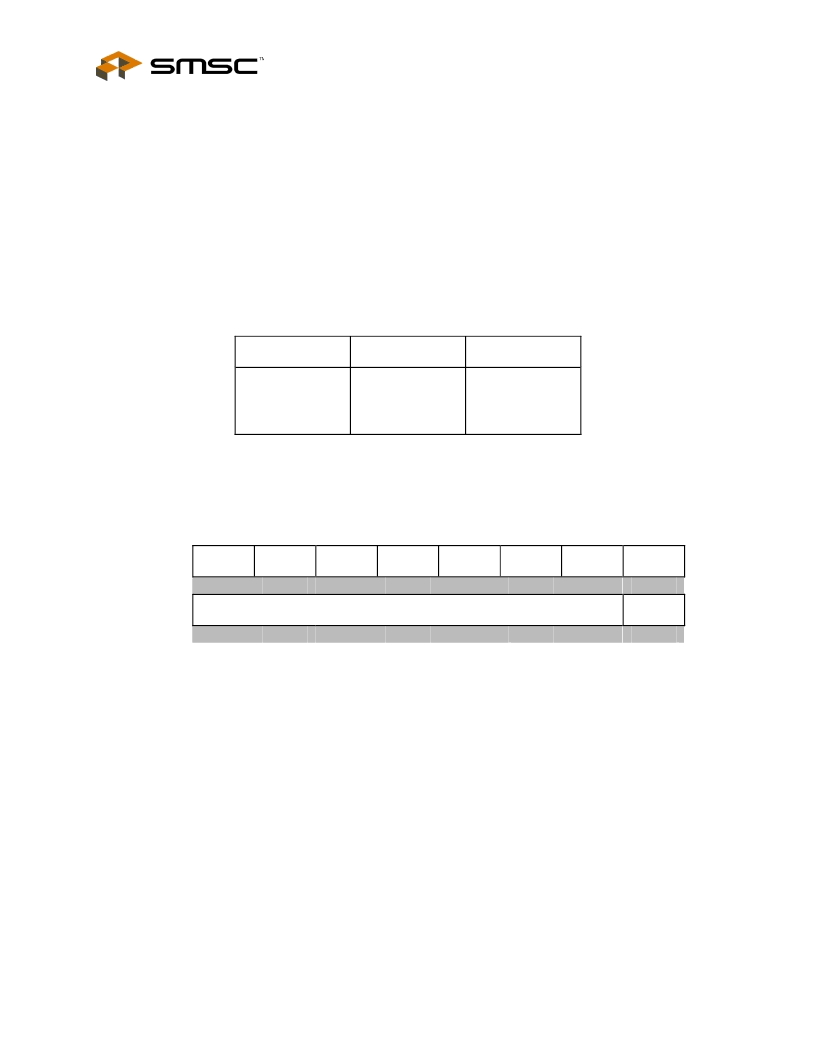

INT SEL1-0 - Used to select one out of four interrupt pins. The three unused interrupts are tristated.

INT SEL1

INT SEL0

INTERRUPT PIN

USED

INTR0

INTR1

INTR2

INTR3

0

0

1

1

0

1

0

1

BANK 1

OFFSET

2

NAME

TYPE

SYMBOL

BAR

BASE ADDRESS REGISTER

READ/WRITE

This register holds the I/O address decode option chosen for the LAN91C100FD. It is part of the EEPROM

saved setup and is not usually modified during run-time.

HIGH

BYTE

LOW

BYTE

A15

A14

A13

A9

A8

A7

A6

A5

0

0

0

1

1

0

0

0

1

Reserved

0

0

0

0

0

0

0

1

A15 - A13 and A9 - A5 - These bits are compared against the I/O address on the bus to determine the

IOBASE for the LAN91C100FD‘s registers. The 64k I/O space is fully decoded by the LAN91C100FD

down to a 16 location space, therefore the unspecified address lines A4, A10, A11 and A12 must be all

zeros.

All bits in this register are loaded from the serial EEPROM. The I/O base decode defaults to 300h

(namely, the high byte defaults to 18h).

Reserved - Must be 0.

BANK 1

OFFSET

4 THROUGH 9

NAME

TYPE

SYMBOL

IAR

INDIVIDUAL ADDRESS

REGISTERS

READ/WRITE

These registers are loaded starting at word location 20h of the EEPROM upon hardware reset or

EEPROM reload. The registers can be modified by the software driver, but a STORE operation will not

modify the EEPROM Individual Address contents. Bit 0 of Individual Address 0 register corresponds to the

first bit of the address on the cable.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN91C100FDREVD | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100FDREVB | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100FDTQFP | FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100 | FEAST⑩ Fast Ethernet Controller |

| LAN91C110 | FEAST FAST ETHERNET CONTROLLER FOR PCMCIA AND GENERIC 16-BIT APPLICATIONS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN91C100-FD | 制造商:SMSC 制造商全稱(chēng):SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

| LAN91C100FD(208PQFP) | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:LAN Node Controller |

| LAN91C100FD(208TQFP) | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:LAN Node Controller |

| LAN91C100FD_06 | 制造商:SMSC 制造商全稱(chēng):SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

| LAN91C100FD_0601 | 制造商:SMSC 制造商全稱(chēng):SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。