- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358742 > LAN91C100FD(208PQFP) LAN Node Controller PDF資料下載

參數(shù)資料

| 型號(hào): | LAN91C100FD(208PQFP) |

| 英文描述: | LAN Node Controller |

| 中文描述: | 網(wǎng)絡(luò)節(jié)點(diǎn)控制器 |

| 文件頁數(shù): | 24/55頁 |

| 文件大小: | 482K |

| 代理商: | LAN91C100FD(208PQFP) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

FEAST Fast Ethernet Controller

for PCMCIA and Generic 16-Bit Applications

SMSC DS – LAN91C110 REV. B

Page 24

Rev. 09/05/02

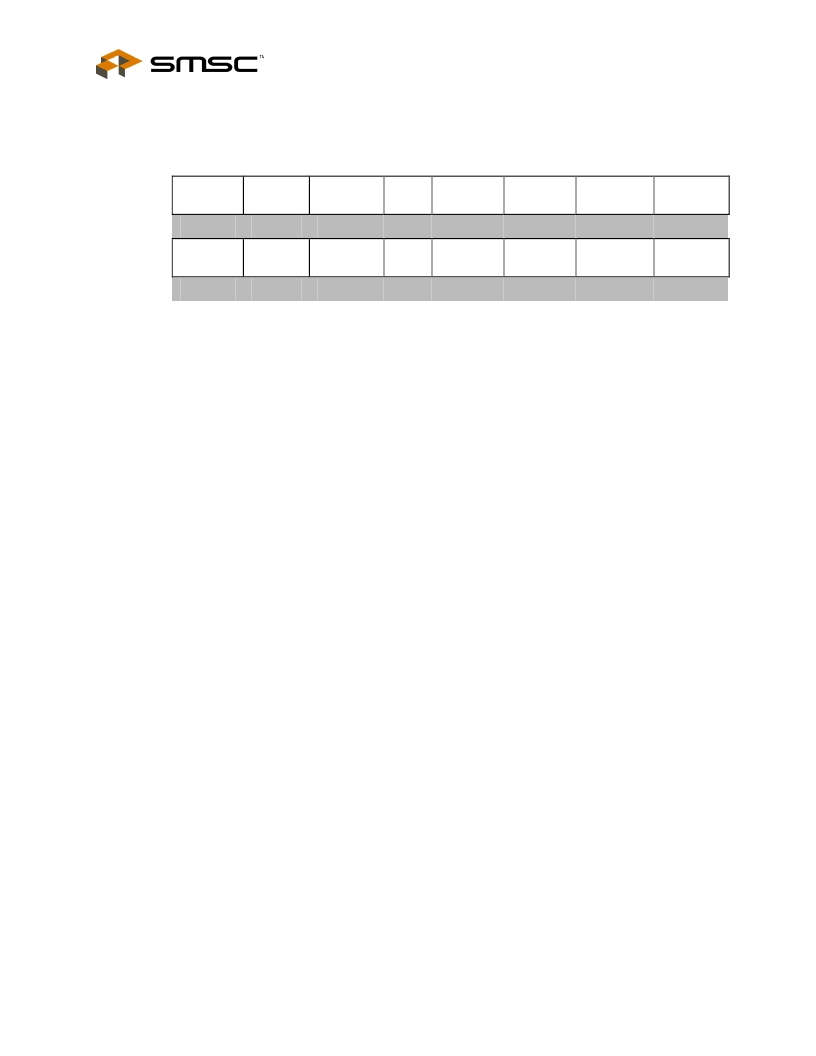

BANK 1

OFFSET

NAME

TYPE

SYMBOL

CTR

C

CONTROL REGISTER

READ/WRITE

HIGH BYTE

Reserved

RCV_

BAD

Reserved

1

AUTO

RELEASE

Reserved

1

Reserved

0

0

0

1

0

0

1

0

LOW BYTE

LE

ENABLE

CR

ENABLE

TE

ENABLE

1

Reserved

Reserved

Reserved

Reserved

0

0

0

1

0

0

0

0

RCV_BAD - When set, bad CRC packets are received. When clear bad CRC packets do not generate interrupts and their

memory is released.

AUTO RELEASE - When set, transmit pages are released by transmit completion if the transmission was successful

(when TX_SUC is set). In that case there is no status word associated with its packet number, and successful packet

numbers are not even written into the TX COMPLETION FIFO. A sequence of transmit packets will generate an interrupt

only when the sequence is completely transmitted (TX EMPTY INT will be set), or when a packet in the sequence

experiences a fatal error (TX INT will be set). Upon a fatal error TXENA is cleared and the transmission sequence stops.

The packet number that failed, is present in the FIFO PORTS register, and its pages are not released, allowing the CPU

to restart the sequence after corrective action is taken.

LE ENABLE - Link Error Enable. When set it enables the LINK_OK bit transition as one of the interrupts merged into the

EPH INT bit. Clearing the LE ENABLE bit after an EPH INT interrupt, caused by a LINK_OK transition, will acknowledge

the interrupt. LE ENABLE defaults low (disabled).

CR ENABLE - Counter Roll over Enable. When set, it enables the CTR_ROL bit as one of the interrupts merged into the

EPH INT bit. Reading the COUNTER register after an EPH INT interrupt caused by a counter rollover, will acknowledge

the interrupt. CR ENABLE defaults low (disabled).

TE ENABLE - Transmit Error Enable. When set it enables Transmit Error as one of the interrupts merged into the EPH

INT bit. An EPH INT interrupt caused by a transmitter error is acknowledged by setting TXENA bit in the TCR register to 1

or by clearing the TE ENABLE bit. TE ENABLE defaults low (disabled). Transmit Error is any condition that clears TXENA

with TX_SUC staying low as described in the EPHSR register.

Reserved 2-0: These reserved bits must always be written to as zero(0).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN91C94 | ISA/PCMCIA SINGLE CHIP ETHERNET CONTROLLER WITH RAM |

| LAN91C110TQFP | FEAST FAST ETHERNET CONTROLLER FOR PCMCIA AND GENERIC 16-BIT APPLICATIONS |

| LAN91C96I | NON-PCI SINGLE-CHIP FULL DUPLES ETHERNET CONTROLLER |

| LAN91C96I-MS | NON-PCI SINGLE-CHIP FULL DUPLES ETHERNET CONTROLLER |

| LAN91C96I-MU | NON-PCI SINGLE-CHIP FULL DUPLES ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN91C100FDQFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:SMSC 功能描述: |

| LAN91C100FDREVB | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100FDREVD | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST FAST ETHERNET CONTROLLER WITH FULL DUPLEX CAPABILITY |

| LAN91C100-FD-SS | 制造商:SMSC 制造商全稱:SMSC 功能描述:FEAST Fast Ethernet Controller with Full Duplex Capability |

| LAN91C100FD-SS | 功能描述:以太網(wǎng) IC Non-PCI 10/100 Ethernet MAC RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。