- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383254 > L9352B (意法半導(dǎo)體) CHOKE, COM/ASYM MODE 2X1.1MH 2A PDF資料下載

參數(shù)資料

| 型號(hào): | L9352B |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | CHOKE, COM/ASYM MODE 2X1.1MH 2A |

| 中文描述: | 智能四(2X5A/2X2.5A)的低邊開關(guān) |

| 文件頁(yè)數(shù): | 11/21頁(yè) |

| 文件大小: | 611K |

| 代理商: | L9352B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

11/21

L9352B

1.7

The drift detection is used to compare the two regulated channels during regulation. This “Drift” test compares

the output PWM of the regulators. The resistivity of the load influences the output PWM. The approximated for-

mula for the output current below shows the dependency of the load resistor to the output PWM. In this formula

the energy reduction during the recirculation is not taken into account. The real output PWM is higher. The test-

mode is enabled with IN, EN and TEST high. With an identical 2kHz PWM-Signal connected to the IN-inputs

the output PWM must be in a range of ±14.3%. If the difference between the two on-times is more than ±14.3%

of the expected value an error is detected and monitored by the status outputs, in the same way as described

above, but a drift error will not be registered and also not delayed with T

D

as other errors

Drift Detection (regulated channels only)

A 7bit output-PWM-register is used for the comparison. The register with the lower value is subtracted from the

higher one. This result is multiplied by four and compared with the higher value.

1.8

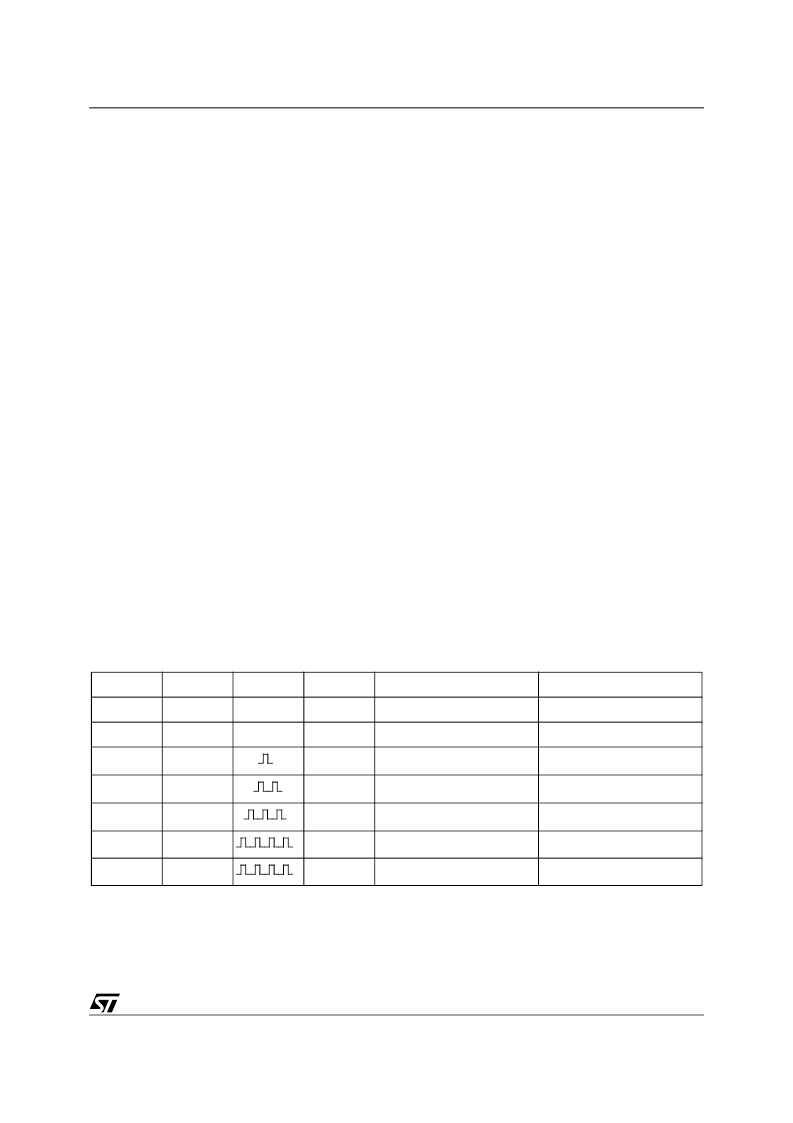

The test pin is also used to test the regulated channels in the production. With a special sequence on this pin

the power stages of the regulated channels can be controlled direct from the input. No status feedback of the

regulated channels is given. The status output is clocked by the regulator logic. The output sequence is a indi-

cation of a proper logic functionality. The following table shows the functionality of this special test mode

Other Test modes

For more details about the test lcondition four see timing diagram.

EN

IN

TEST

OUT

STATUS

Note

1

X

X

X

X

disable test mode

1

1

1

on

1

Drift mode

0

X

off

test pattern

test condition one

0

X

off

test pattern

test condition two

0

X

off

test pattern

test condition three

0

0

off

test pattern

test condition four

0

1

on

test pattern

test condition four

IOUT

RL

+

RON

----------------------------

PWM

=

Drift Definition:

Drift = PWM(1+E) - PWM (1-E) = 2PWM E

Drift * 4 < PWM (1+E)

with E >14.3% a drift is detected

E.. not correlated Error of the channels

%PWM ... Corresponding ideal output PWM to a given input PWM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L9352 | CAP CER 1800PF 3.15KVDC R3 RAD |

| L9352-DIE1 | INTELLIGENT QUAD 2X5A/2X2.5A LOW-SIDE SWITCH |

| L9363 | QUAD INTEGRATED LOW SIDE DRIVER |

| L9377 | DUAL INTELLIGENT POWER LOW SIDE SWITCH |

| L9377DIE1 | DUAL INTELLIGENT POWER LOW SIDE SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L9352B-DIE1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:INTELLIGENT QUAD (2X5A/2X2.5A) LOW-SIDE SWITCH |

| L9352B-LF | 功能描述:電源開關(guān) IC - 配電 Intelligent Quad 2x5A/2x2.5A Switch RoHS:否 制造商:Exar 輸出端數(shù)量:1 開啟電阻(最大值):85 mOhms 開啟時(shí)間(最大值):400 us 關(guān)閉時(shí)間(最大值):20 us 工作電源電壓:3.2 V to 6.5 V 電源電流(最大值): 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-23-5 |

| L9352B-TR-LF | 功能描述:電源開關(guān) IC - 配電 Intelligent Quad 2x5A/2x2.5A Switch RoHS:否 制造商:Exar 輸出端數(shù)量:1 開啟電阻(最大值):85 mOhms 開啟時(shí)間(最大值):400 us 關(guān)閉時(shí)間(最大值):20 us 工作電源電壓:3.2 V to 6.5 V 電源電流(最大值): 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-23-5 |

| L9352-DIE1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:INTELLIGENT QUAD 2X5A/2X2.5A LOW-SIDE SWITCH |

| L9353M | 制造商:EPCOS 制造商全稱:EPCOS 功能描述:IF Filter for Audio Applications |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。