- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377592 > L29C525 (Logic Devices Incorporated) Dual Pipeline Register PDF資料下載

參數(shù)資料

| 型號(hào): | L29C525 |

| 廠商: | Logic Devices Incorporated |

| 英文描述: | Dual Pipeline Register |

| 中文描述: | 雙管道注冊(cè) |

| 文件頁(yè)數(shù): | 1/6頁(yè) |

| 文件大?。?/td> | 172K |

| 代理商: | L29C525 |

DEVICES INCORPORATED

L29C525

Dual Pipeline Register

Dual Pipeline Register

Pipeline Registers

03/

23

/2000–LDS.29C525-G

1

K

Dual 8-Deep Pipeline Register

K

Configurable to Single 16-Deep

K

Low Power CMOS Technology

K

Replaces AMD Am29525

K

Load, Shift, and Hold Instructions

K

Separate Data In and Data Out Pins

K

Three-State Outputs

K

Package Styles Available:

28-pin Plastic DIP

28-pin Plastic LCC, J-Lead

FEATURES

DESCRIPTION

DEVICES INCORPORATED

The

L29C525

is a high-speed, low

power CMOS pipeline register. It is

pin-for-pin compatible with the AMD

Am29525. The L29C525 can be

configured as two independent 8-level

pipelines or as a single 16-level

pipeline. The configuration imple-

mented is determined by the instruc-

tion code (I

1-0

) as shown in Table 2.

The I

1-0

instruction code controls the

internal routing of data and loading of

each register. For instruction I

1-0

= 00

(Push A and B), data applied at the

D

7-0

inputs is latched into register A0

on the rising edge of CLK. The

contents of A0 simultaneously move

to register A1, A1 moves to A2, and so

on. The contents of register A7 are

wrapped back to register B0. The

registers on the B side are similarly

shifted, with the contents of register

B7 lost.

Instruction I

1-0

= 01 (Push B) acts

similarly to the Push A and B

instruction, except that only the B side

registers are shifted. The input data is

applied to register B0, and the

contents of register B7 are lost. The

contents of the A side registers are

unaffected. Instruction I

1-0

= 10 (Push

A) is identical to the Push B

instruction, except that the A side

registers are shifted and the B side

registers are unaffected.

Instruction I

1-0

= 11 (Hold) causes no

internal data movement. It is equiva-

lent to preventing the application of a

clock edge to any internal register.

The contents of any of the registers is

selectable at the output through the

use of the S

3-0

control inputs. The

independence of the I and S control

lines allows simultaneous reading and

writing. Encoding for the S

3-0

controls

is given in Table 3.

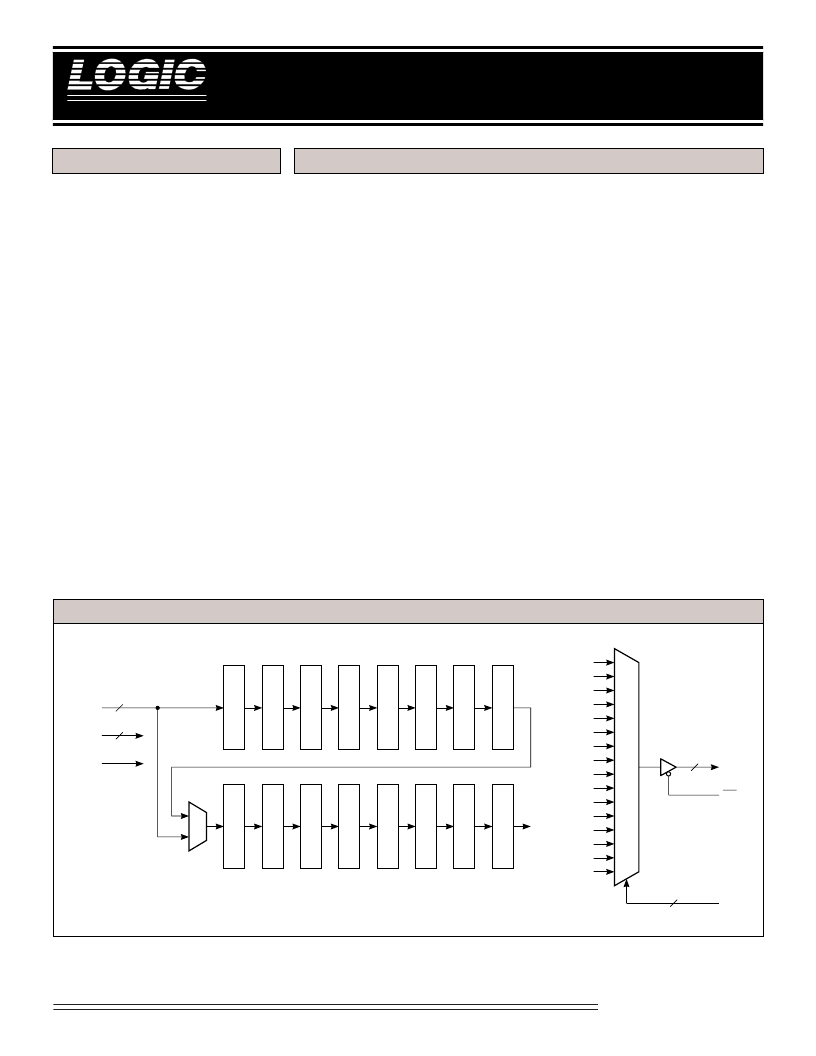

L29C525 B

LOCK

D

IAGRAM

8

OE

Y

7-0

D

7-0

I

1-0

CLK

M

4

M

2

S

3-0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

A0

A1

A2

A3

A4

A5

A6

A7

B0

B1

B2

B3

B4

B5

B6

B7

8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L29C525JC15 | Dual Pipeline Register |

| L29C525JC20 | Dual Pipeline Register |

| L2N3904 | General Purpose Transistors NPN Silicon |

| L2N5401 | Amplifier Transistors PNP Silicon |

| L2N7002LT1 | Small Signal MOSFET 115 mAmps, 60 Volts |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L29C525CC15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Pipeline Register |

| L29C525CC20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Pipeline Register |

| L29C525CM20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Pipeline Register |

| L29C525CM25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Pipeline Register |

| L29C525CMB20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Pipeline Register |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。