- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11573 > KSZ8841-16MBLI (Micrel Inc)IC MAC CTRLR 8/16BIT 100-LBGA PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8841-16MBLI |

| 廠商: | Micrel Inc |

| 文件頁數(shù): | 34/105頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC MAC CTRLR 8/16BIT 100-LBGA |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 控制器類型: | 以太網(wǎng)控制器,MAC |

| 接口: | 總線 |

| 電源電壓: | 3.1 V ~ 3.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LBGA |

| 供應(yīng)商設(shè)備封裝: | 100-LFBGA |

| 包裝: | 散裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁

Micrel, Inc.

KSZ8841-16/32 MQL/MVL/MBL

October 2007

34

M9999-102207-1.6

Signal

Type

(1)

Function

Common Signals

A[15:1]

I

Address

AEN

I

Address Enable

Address Enable asserted indicates memory address on the bus for DMA access

and since the device is an I/O device, address decoding is only enabled when AEN

is Low.

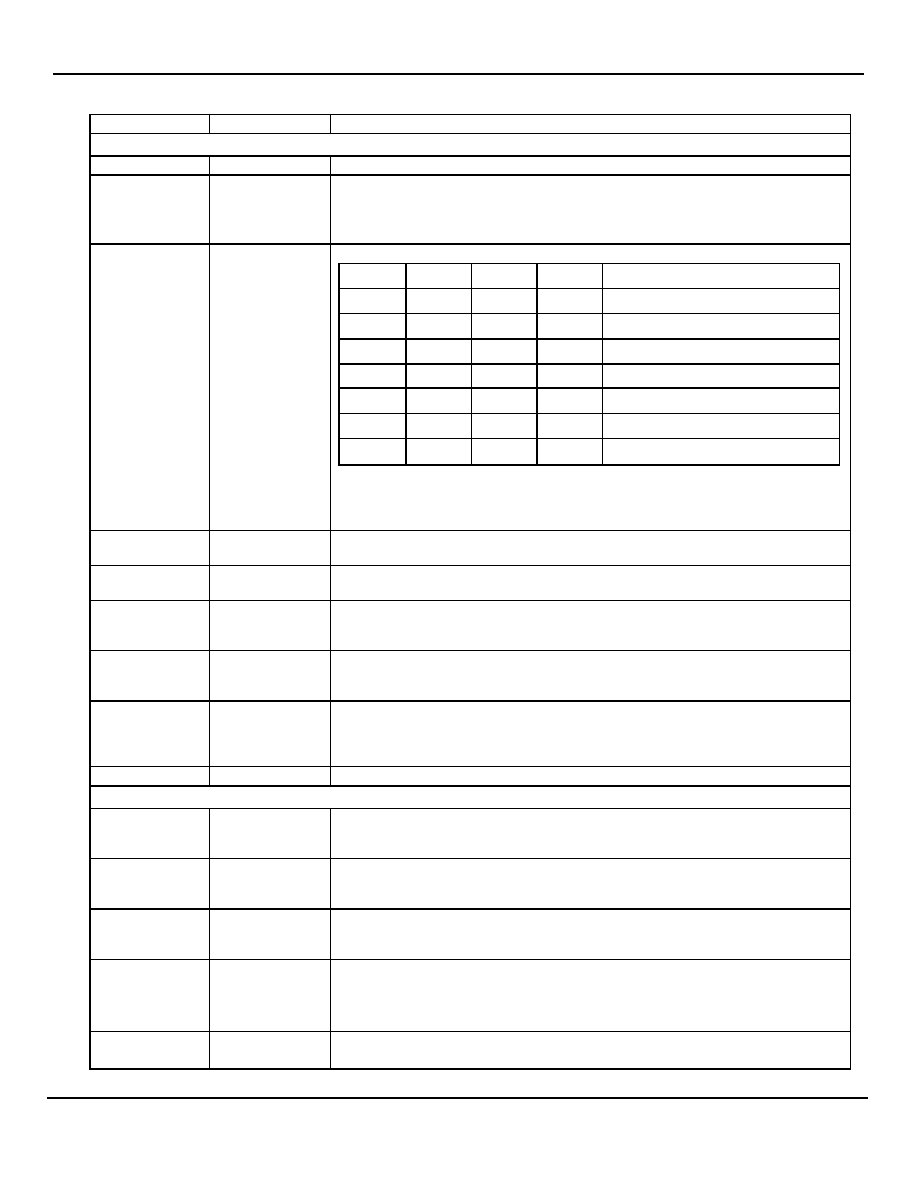

BE3N, BE2N,

BE1N, BE0N

I

Byte Enable

BE0N

BE1N

BE2N

BE3N

Description

0

32-bit access

0

1

Lower 16-bit (D[15:0]) access

1

0

Higher 16-bit (D[31:16]) access

0

1

Byte 0 (D[7:0]) access

1

0

1

Byte 1 (D[15:8]) access

1

0

1

Byte 2 (D[23:16]) access

1

0

Byte 3 (D[31:24]) access

Note 1: BE3N, BE2N, BE1N and BE0N are ignored when DATACSN is low because

32 bit transfers are assumed.

Note 2: BE2N and BE3N are valid only for the KSZ8841-32 mode, and are No

Connect for the KSZ8841-16 mode.

D[31:16]

I/O

Data

For KSZ8841M-32 mode only.

D[15:0]

I/O

Data

For both KSZ8841-32 and KSZ8841-16 Modes

ADSN

I

Address Strobe

The rising edge of ADSN is used to latch A[15:1], AEN, BE3N, BE2N, BE1N and

BE0N.

LDEVN

O

Local Device

This signal is a combinatorial decode of AEN and A[15:4]. This A[15:4] is used to

compare against the Base Address Register.

DATACSN

I

Data Register Chip Select (For KSZ8841-32MQL Mode only)

This signal is used for central decoding architecture (mostly for embedded

application). When asserted, the device’s local decoding logic is ignored and the 32-

bit access to QMU Data Register is assumed.

INTR

O

Interrupt

Synchronous Transfer Signals

VLBUSN

I

VLBUS

VLBUSN = 0, VLBus-like cycle.

VLBUSN = 1, burst cycle (both host/system and KSZ8841M can insert wait state)

CYCLEN

I

CYCLEN

For VLBus-like access: used to sample SWR when asserted.

For burst access: used to connect to IOWC# bus signal to indicate burst write.

SWR

I

Write/Read

For VLBus-like access: used to indicate write (High) or read (Low) transfer.

For burst access: used to connect to IORC# bus signal to indicate burst read.

SRDYN

O

Synchronous Ready

For VLBus-like access: exactly the same signal definition of nSRDY in VLBus.

For burst access: insert wait state by KSZ8841M whenever necessary during the

Data Register access.

RDYRTNN

I

Ready Return

For VLBus-like access: exactly like RDYRTNN signal in VLBus to end the cycle.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KSZ8842-16MVL | IC ETHERNET SW 2PORT BUS 128LQFP |

| V300A12C400BL3 | CONVERTER MOD DC/DC 12V 400W |

| PIC16F687-E/P | IC PIC MCU FLASH 2KX14 20DIP |

| V300A12C400B3 | CONVERTER MOD DC/DC 12V 400W |

| V300A12C400B2 | CONVERTER MOD DC/DC 12V 400W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8841-16MQL | 功能描述:以太網(wǎng) IC Single Ethernet Port + Generic (8, 16-bit) bus interface( Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8841-16MQL A6 | 功能描述:IC MAC CTRLR 8/16BIT 128-PQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| KSZ8841-16MQL-EVAL | 功能描述:以太網(wǎng)開發(fā)工具 KSZ8841-16MQL Evaluation Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| KSZ8841-16MVL | 功能描述:以太網(wǎng) IC Single Ethernet Port + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8841-16MVL TR | 功能描述:以太網(wǎng) IC Single Ethernet Port + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。