- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374356 > KM48C8104B (SAMSUNG SEMICONDUCTOR CO. LTD.) 8M x 8bit CMOS Dynamic RAM with Extended Data Out(8M x 8位CMOS 動態(tài)RAM(帶擴(kuò)展數(shù)據(jù)輸出)) PDF資料下載

參數(shù)資料

| 型號: | KM48C8104B |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 8M x 8bit CMOS Dynamic RAM with Extended Data Out(8M x 8位CMOS 動態(tài)RAM(帶擴(kuò)展數(shù)據(jù)輸出)) |

| 中文描述: | 8米× 8位的擴(kuò)展數(shù)據(jù)輸出的CMOS動態(tài)RAM(8米× 8位的CMOS動態(tài)隨機(jī)存儲器(帶擴(kuò)展數(shù)據(jù)輸出)) |

| 文件頁數(shù): | 7/21頁 |

| 文件大?。?/td> | 366K |

| 代理商: | KM48C8104B |

KM48C8004B,

KM48C8104B

CMOS DRAM

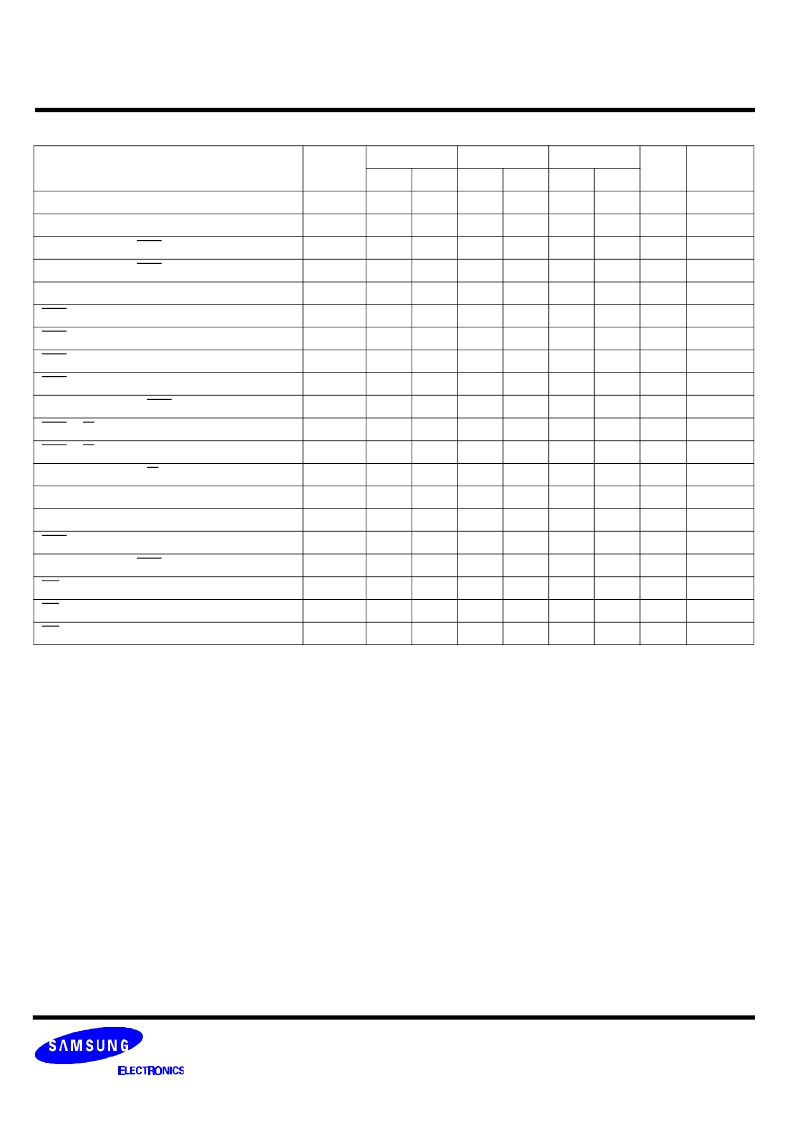

TEST MODE CYCLE

Parameter

Symbol

-45

-5

-6

Units

Note

Min

Max

Min

Max

Min

Max

Random read or write cycle time

t

RC

79

89

109

ns

Read-modify-write cycle time

t

RWC

110

121

145

ns

Access time from RAS

t

RAC

50

55

65

ns

3,4,10,12

Access time from CAS

t

CAC

17

18

20

ns

3,4,5,12

Access time from column address

t

AA

28

30

35

ns

3,10,12

RAS pulse width

t

RAS

50

10K

55

10K

65

10K

ns

CAS pulse width

t

CAS

12

10K

13

10K

15

10K

ns

RAS hold time

t

RSH

18

18

20

ns

CAS hold time

t

CSH

39

43

50

ns

Column Address to RAS lead time

t

RAL

28

30

35

ns

CAS to W delay time

t

CWD

29

35

39

ns

7

RAS to W delay time

t

RWD

62

72

84

ns

7

Column Address to W delay time

t

AWD

40

47

54

ns

7

Hyper Page cycle time

t

HPC

22

25

30

ns

13

Hyper Page read-modify-write cycle time

t

HPRWC

52

53

61

ns

13

RAS pulse width (Hyper page cycle)

t

RASP

50

200K

55

200K

65

200K

ns

Access time from CAS precharge

t

CPA

29

33

40

ns

3

OE access time

t

OEA

17

18

20

ns

OE to data delay

t

OED

13

18

20

ns

OE command hold time

t

OEH

13

18

20

ns

( Note 11 )

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM48S16030A | 128Mbit SDRAM 4M x 8Bit x 4 Banks Synchronous DRAM LVTTL |

| KM48S16030B | 128Mbit SDRAM 4M x 8Bit x 4 Banks Synchronous DRAM LVTTL |

| KM48S16030 | 4M x 8Bit x 4 Banks Synchronous DRAM |

| KM48S32230A | 8M x 8Bit x 4 Banks Synchronous DRAM(8M x 8位 x 4組同步動態(tài)RAM) |

| KM48S8030B | 2M x 8Bit x 4 Banks Synchronous DRAM(2M x 8位 x 4組同步動態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM-48F 50UA DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 0-50MV DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 100-0-100UA DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 100MA DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 100UA DC | 制造商:Fujita Electric 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。