- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373155 > KM416RD16D (SAMSUNG SEMICONDUCTOR CO. LTD.) 15VPP 86DB 2 TERM CERAM BUZZER PDF資料下載

參數(shù)資料

| 型號(hào): | KM416RD16D |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 15VPP 86DB 2 TERM CERAM BUZZER |

| 中文描述: | 128/144Mbit RDRAM的256 × 16/18位× 2 * 16屬銀行直接RDRAMTM |

| 文件頁(yè)數(shù): | 29/64頁(yè) |

| 文件大小: | 4052K |

| 代理商: | KM416RD16D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

Page 26

KM416RD8AC(D)/KM418RD8AC(D)

Direct RDRAM

Rev. 1.01 Oct. 1999

Control Register Transactions

The RDRAM has two CMOS input pins SCK and CMD and

two CMOS input/output pins SIO0 and SIO1. These provide

serial access to a set of control registers in the RDRAM.

These control registers provide configuration information to

the controller during the initialization process. They also

allow an application to select the appropriate operating mode

of the RDRAM.

SCK (serial clock) and CMD (command) are driven by the

controller to all RDRAMs in parallel. SIO0 and SIO1 are

connected (in a daisy chain fashion) from one RDRAM to

the next. In normal operation, the data on SIO0 is repeated

on SIO1, which connects to SIO0 of the next RDRAM (the

data is repeated from SIO1 to SIO0 for a read data packet).

The controller connects to SIO0 of the first RDRAM.

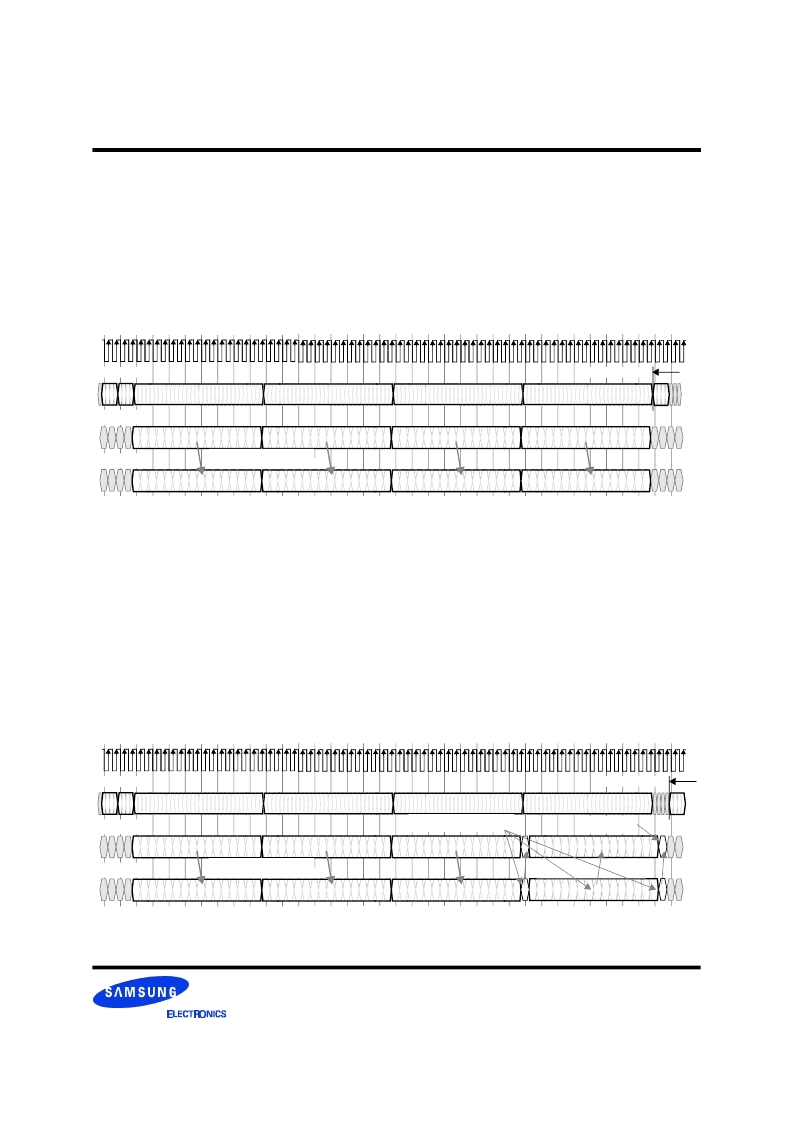

Write and read transactions are each composed of four

packets, as shown in Figure 23 and Figure 24. Each packet

consists of 16 bits, as summarized in Table 14 and Table 15.

The packet bits are sampled on the falling edge of SCK. A

transaction begins with a SRQ (Serial Request) packet. This

packet is framed with a 11110000 pattern on the CMD input

(note that the CMD bits are sampled on both the falling edge

and the rising edge of SCK). The SRQ packet contains the

SOP3..SOP0 (Serial Opcode) field, which selects the trans-

action type. The SDEV5..SDEV0 (Serial Device address)

selects one of the 32 RDRAMs. If SBC (Serial Broadcast) is

set, then all RDRAMs are selected. The SA (Serial Address)

packet contains a 12 bit address for selecting a control

register.

A write transaction has a SD (Serial Data) packet next. This

contains 16 bits of data that is written into the selected

control register. A SINT (Serial Interval) packet is last,

providing some delay for any side-effects to take place. A

read transaction has a SINT packet, then a SD packet. This

provides delay for the selected RDRAM to access the

control register. The SD read data packet travels in the oppo-

site direction (towards the controller) from the other packet

types. The SCK cycle time will accomodate the total delay.

Figure 23: Serial Write (SWR) Transaction to Control Register

SRQ - SWR command

1111

00000000...00000000

SRQ - SWR command

0000

SA

SA

SD

SD

SINT

SINT

00000000...00000000

00000000...00000000

00000000...00000000

SCK

CMD

SIO0

SIO1

T

4

T

36

T

20

T

52

T

68

Each packet is repeated

from SIO0 to SIO1

1

1

1

1

0

0

0

0

1111

next transaction

Figure 24: Serial Read (SRD) Transaction Control Register

SRQ - SRD command

1111

00000000...00000000

SRQ - SRD command

0000

SA

SA

SINT

SINT

SD

SD

00000000...00000000

00000000...00000000

00000000...00000000

SCK

CMD

SIO0

SIO1

T

4

T

36

T

20

T

52

T

68

First 3 packets are repeated

from SIO0 to SIO1

non-addressed RDRAMs pass

0/SD15..SD0/0 from SIO1 to SIO0

1

1

1

1

0

0

0

0

1111

next transaction

0

0

controller drives

0 on SIO0

0

0

addressed RDRAM drives

0/SD15..SD0/0 on SIO0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM416RD2AC | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2AD | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2C | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2D | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD32AC | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM416RD2AC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2AD | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD2D | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD32AC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。