- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄361007 > IVC102 PRECISION SWITCHED INTEGRATOR TRANSIMPEDANCE AMPLIFIER PDF資料下載

參數(shù)資料

| 型號(hào): | IVC102 |

| 元件分類(lèi): | 跨阻放大器 |

| 英文描述: | PRECISION SWITCHED INTEGRATOR TRANSIMPEDANCE AMPLIFIER |

| 中文描述: | 精密投切積分器互阻抗放大器 |

| 文件頁(yè)數(shù): | 8/10頁(yè) |

| 文件大小: | 124K |

| 代理商: | IVC102 |

8

IVC102

The input current, I

IN

, is shown as a conventional current

flowing into pin 2 in this diagram but the input current could

be bipolar (positive or negative). Current flowing out of pin

2 would produce a positive-ramping V

O

.

The timing sequence proceeds as follows:

Reset Period

The integrator is reset by closing switch S

2

with S

1

open. A

10

μ

s reset time is recommended to allow the op amp to slew

to 0V and settle to its final value.

Pre-Integration Hold

S

2

is opened, holding V

O

constant for 10

μ

s prior to integra-

tion. This pre-integration hold period assures that S

2

is fully

open before S

1

is closed so that no input signal is lost. A

minimum of 1

μ

s is recommended to avoid switching over-

lap. The 10

μ

s hold period shown in Figure 3b also allows an

a/d converter measurement to be made at point A. The

purpose of this measurement at A is discussed in the “Offset

Errors” section.

Integration on C

INT

Integration of the input current on C

INT

begins when S

1

is

closed. An immediate step output voltage change occurs as

the charge that was stored on the input sensor capacitance is

transferred to C

INT

. Although this period of charging C

INT

occurs only while S

1

is closed, the charge transferred as S

1

is closed causes the

effective

integration time to be equal to

the complete conversion period—see Figure 3b.

The integration period could range from 100

μ

s to many

minutes, depending on the input current and C

INT

value.

While S

1

is closed, I

IN

charges C

INT

, producing a negative-

going ramp at the integrator output voltage, V

O

. The output

voltage at the end of integration is proportional to the

average input current throughout the complete conversion

cycle, including the integration period, reset and both hold

periods.

Hold Period

Opening S

1

halts integration on C

INT

. Approximately 5

μ

s

after S

1

is opened, the output voltage is stable and can be

measured (at point B). The hold period is 10

μ

s in this

example. C

INT

remains charged until a S

2

is again closed, to

reset for the next conversion cycle.

In this timing example, S

1

is open for a total of 30

μ

s. During

this time, signal current from the sensor charges the sensor

source capacitance. Care should be used to assure that the

voltage developed on the sensor does not exceed approxi-

mately 200mV during this time. The I

IN

terminal, pin 2, is

internally clamped with diodes. If these diodes forward bias,

signal current will flow to ground and will not be accurately

integrated.

A maximum of 333nA signal current could be accurately

integrated on a 50pF sensor capacitance for 30

μ

s before

200mV would be developed on the sensor.

I

MAX

= (50pF) (200mV)/30

μ

s = 333nA

OFFSET ERRORS

Figure 3c shows the effect on V

O

due to op amp input offset

voltage, input bias current and switch charge injection. It

assumes zero input current from the sensor. The various

offsets and charge injection (

Q) jumps shown are typical of

that seen with a 50pF source capacitance. The specified

“transfer function offset voltage” is the voltage measured

during the hold period at B. Transfer function offset voltage

is dominated by the charge injection of S

2

opening and op

amp V

OS

. The opening and closing charge injections of S

1

are very nearly equal and opposite and are not significant

contributors.

Note that using a two-point difference measurement at A

and B can dramatically reduce offset due to op amp V

OS

and

S

2

charge injection. The remaining offset with this B-A

measurement is due to op amp input bias current charging

C

INT

. This error is usually very small and is exaggerated in

the figure.

DIGITAL SWITCH INPUTS

The digital control inputs to S

1

and S

2

are compatible with

standard CMOS or TTL logic. Logic input pins 11 and 12

are high impedance and the threshold is approximately 1.4V

relative to Digital Ground, pin 13. A logic “l(fā)ow” closes the

switch.

Use care in routing these logic signals to their respective

input pins. Capacitive coupling of logic transitions to sensi-

tive input nodes (pins 2 through 6) and to the positive power

supply (pin 14) will dramatically increase charge injection

and produce errors. Route these circuit board traces over a

ground plane (digital ground) and route digital ground traces

between logic traces and other critical traces for lowest

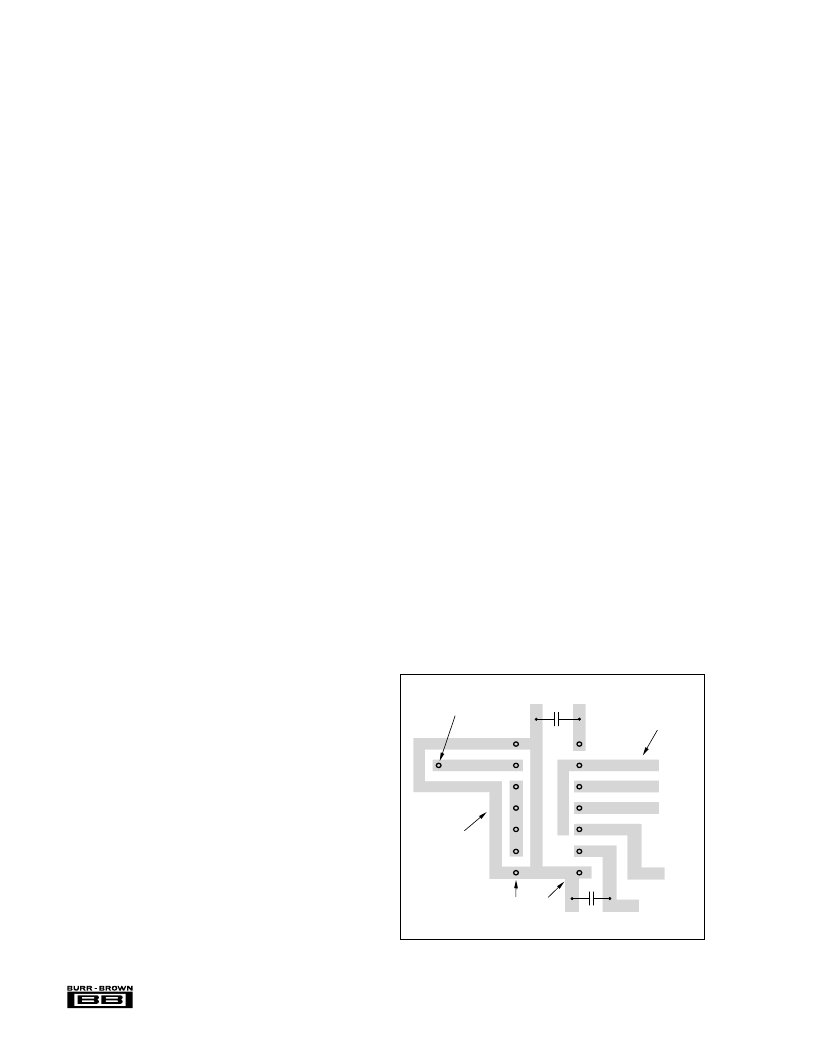

charge injection. See Figure 4.

5V logic levels are generally satisfactory. Lower voltage

logic levels may help reduce charge injection errors, de-

pending on circuit layout. Logic high voltages greater than

5.5V, or higher than the V+ supply are not recommended.

FIGURE 4. Circuit Board Layout Techniques.

Input trace guarded

all the way to sensor.

Switch logic inputs

guarded by digital

ground.

Analog

Ground

Digital

Ground

Pins 7 and 8 have no internal

connection but are connected to

ground for lowest noise pickup.

V+

Input nodes

guarded by

analog ground.

V–

V

O

S

1

S

2

14

8

7

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IVC102P | PRECISION SWITCHED INTEGRATOR TRANSIMPEDANCE AMPLIFIER |

| IVC102U | RES,Carbon Film,15KOhms,350WV,5+/-% Tol |

| IVM-20B-500B | Amplifier. Other |

| IVM-20B-70B | Amplifier. Other |

| IWD1205B | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IVC102P | 制造商:BB 制造商全稱(chēng):BB 功能描述:PRECISION SWITCHED INTEGRATOR TRANSIMPEDANCE AMPLIFIER |

| IVC102U | 功能描述:跨阻抗放大器 Prec Swtched Integ Transimpedance RoHS:否 制造商:Texas Instruments 封裝 / 箱體:SOIC-14 帶寬:3 MHz 工作電源電壓:36 V 電源電流:5.5 mA 工作溫度范圍:- 40 C to + 85 C 封裝:Tube |

| IVC102U | 制造商:Texas Instruments 功能描述:AMP INTEG TRANSIMPEDANCE SOIC14 |

| IVC102U/2K5 | 功能描述:跨阻抗放大器 Prec Swtched Integ Transimpedance RoHS:否 制造商:Texas Instruments 封裝 / 箱體:SOIC-14 帶寬:3 MHz 工作電源電壓:36 V 電源電流:5.5 mA 工作溫度范圍:- 40 C to + 85 C 封裝:Tube |

| IVC102U/2K5G4 | 功能描述:跨阻抗放大器 Prec Swtched Integ Transimpedance RoHS:否 制造商:Texas Instruments 封裝 / 箱體:SOIC-14 帶寬:3 MHz 工作電源電壓:36 V 電源電流:5.5 mA 工作溫度范圍:- 40 C to + 85 C 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。