- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384535 > ISPGDXTMFAMILY (Lattice Semiconductor Corporation) JT 100C 100#22D PIN RECP PDF資料下載

參數(shù)資料

| 型號(hào): | ISPGDXTMFAMILY |

| 廠商: | Lattice Semiconductor Corporation |

| 元件分類: | TVS-瞬態(tài)抑制二極管 |

| 英文描述: | JT 100C 100#22D PIN RECP |

| 中文描述: | 在系統(tǒng)可編程通用數(shù)字CrosspointTM |

| 文件頁數(shù): | 16/25頁 |

| 文件大?。?/td> | 326K |

| 代理商: | ISPGDXTMFAMILY |

16

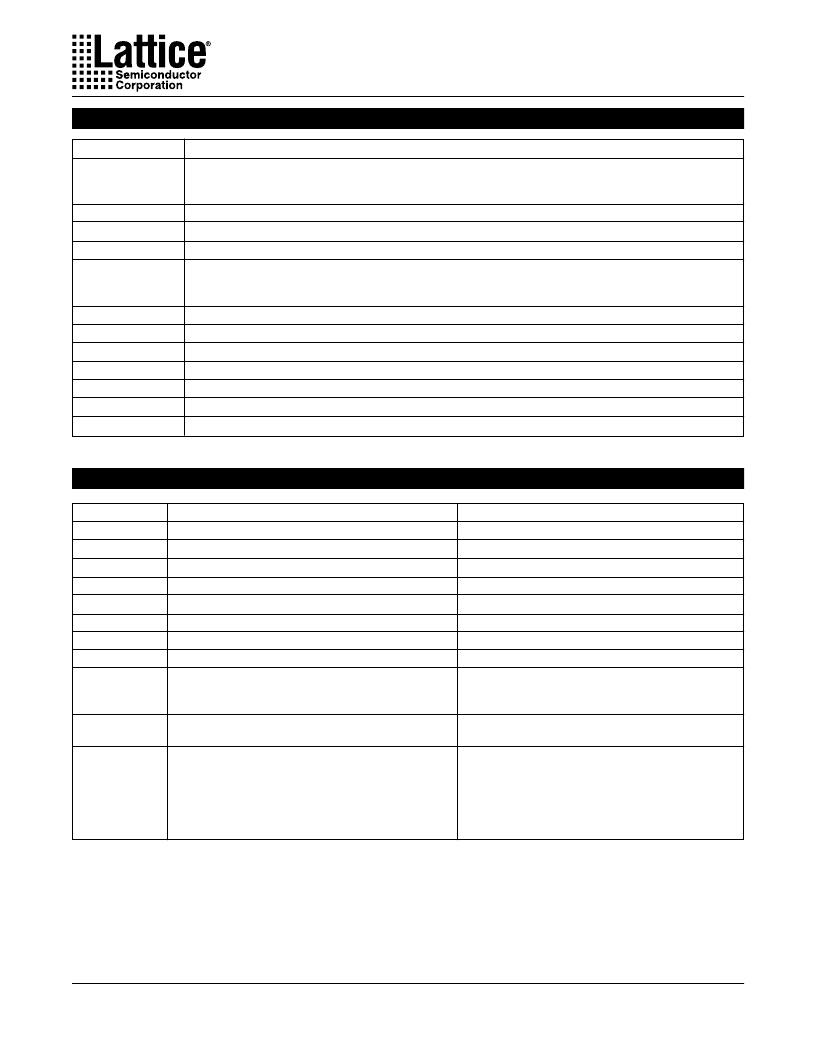

Specifications

ispGDX Family

TOE

RESET

Y0, Y1, Y2, Y3,

BSCAN/

ispEN

TDI/SDI

TCK/SCLK

TMS/MODE

TDO/SDO

GND

178

185

75, 76, 180, 181

183

81

80

79

78

6, 15, 25, 35, 44, 54, 63, 77, 91, 100, 110, 119, 129,

139, 148, 159, 168, 182, 195, 204

A12

D10

V10, Y10, C11, A11

B10

Y12

U11

V11

W11

A1, D4, D8, D13, D17, H4, H17, J9, J10, J11, J12,

K9, K10, K11, K12, L9, L10, L11, L12, M9, M10,

M11, M12, N4, N17, U4, U8, U13, U17

D6, D11, D15, F4, F17, K4, L17, R4, R17, U6, U10,

U15

A2, A6, A7, A10, A15, A19, A20, B1, B2, B4, B11,

B14, B18, B19, B20, C2, C3, C10, C18, D2, D3, D16,

E2, E17, E19, H1, H3, H18, H20, K20, L1, N1, N3,

N18, N20, T2, T4, T19, U5, U18, U19, V3, V14, V18,

V19, W1, W2, W3, W7, W10, W14, W19, W20, Y1,

Y2, Y6, Y9, Y11, Y18, Y20

VCC

1, 17, 33, 49, 65, 89, 105, 121, 137, 153, 170, 184

193

73, 74, 156, 179

NC

1

Signal Descriptions

I/O

Input/Output Pins

–

These are the general purpose bidirectional data pins. When used as outputs, each

may be independently latched, registered or tristated. They can also each assume one other control

function (OE, CLK and MUXsel as described in the text).

Test Output Enable pin

–

This pin tristates all I/O pins when a logic low is driven.

Active LOW Input Pin

–

Resets all I/O register outputs when LOW.

Input Pins

–

Dedicated clock input pins. Each pin can drive any or all I/O cell registers.

Input Pin

–

When HIGH, this pin enables the Boundary Scan Test and Programming Interface. When

LOW, this pin enables the Lattice ISP protocol for programming and tristates all I/O pins, except those

used for the programming interface.

Input/Input Pin

–

Serial data input during ISP programming or Boundary Scan mode.

Input/Input Pin

–

Serial data clock during ISP programming or Boundary Scan mode.

Input/Input Pin

–

Control input during ISP programming or Boundary Scan mode.

Output/Output Pin

–

Serial data output during ISP programming or Boundary Scan mode.

Ground (GND)

Vcc

–

Supply voltage (5V).

No Connect.

TOE

RESET

Y0, Y1, Y2, Y3

BSCAN/

ispEN

TDI/SDI

TCK/SCLK

TMS/MODE

TDO/SDO

GND

VCC

NC

1

Signal Name Description

1. NC pins are not to be connected to any active signals, VCC or GND.

Signal 208-Pin PQFP 272-Ball BGA

1. NC pins are not to be connected to any active signals, VCC or GND.

Signal Locations: ispGDX160/A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPGDX160A-5B272 | In-System Programmable Generic Digital CrosspointTM |

| ISPGDX80VA-7T100 | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPGDX80VA-3T100 | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPGDX80VA-5T100 | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPGDX80VA-5T100I | In-System Programmable 3.3V Generic Digital CrosspointTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPHEADER01 | 制造商:Xeltek Inc 功能描述:ISP10/D10 |

| ISPICR1 | 功能描述:ADAPTER IN-CIRCUIT PROGRAMMING RoHS:否 類別:編程器,開發(fā)系統(tǒng) >> 配件 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program RoHS指令信息:IButton RoHS Compliance Plan 標(biāo)準(zhǔn)包裝:1 系列:- 附件類型:USB 至 1-Wire? RJ11 適配器 適用于相關(guān)產(chǎn)品:1-Wire? 設(shè)備 產(chǎn)品目錄頁面:1429 (CN2011-ZH PDF) |

| ISPL1048E-100LQ | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Density Programmable Logic |

| ISPL1048E-100LQI | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Density Programmable Logic |

| ISPL1048E-100LT | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Density Programmable Logic |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。