- 您現(xiàn)在的位置:買賣IC網(wǎng) > Datasheet目錄40 > ISL61861DCBZ (Intersil)IC USB PWR CTRLR 3A 8SOIC Datasheet資料下載

參數(shù)資料

| 型號: | ISL61861DCBZ |

| 廠商: | Intersil |

| 文件頁數(shù): | 13/18頁 |

| 文件大?。?/td> | 717K |

| 描述: | IC USB PWR CTRLR 3A 8SOIC |

| 標(biāo)準包裝: | 980 |

| 類型: | 熱交換開關(guān) |

| 應(yīng)用: | USB 過電流保護控制器 |

| 內(nèi)部開關(guān): | 是 |

| 電流限制: | 3A |

| 電源電壓: | 2.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 8-SOIC(0.154",3.90mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 8-SOIC |

| 包裝: | 管件 |

ISL6186

13

FN7698.2

November 3, 2011

Application Information

Using the ISL6186XEVAL1Z Platform

General and Biasing Information

There are three evaluation platforms for the ISL6186 family.

There is one for each package style, each with a different

continuous output current level and representing a mix of enable

polarity and output retry or latch options. The standard available

evaluation board options are listed at the end of the Ordering

Information table, which starts on page3. Figure 28A illustrates

the schematic for the 10 Ld DFN ISL61863EVAL1Z. Other than

the unique PGOOD output on the ISL61863 types, all the

schematics and functions are the same across all three package

types. Consult the individual package pinouts on page2 for those

differences.

The evaluation platform is biased and monitored through a few

labeled test points. See Table 1 for test point assignments and

descriptions.

Upon proper bias of the evaluation platform and correct enabling

of the IC, the ISL6186 will have a nominal V

IN

/5.1?/SPAN> load current

that is below the continuous current rating passing through each

enabled switch. See Figures 14 to 16 for typical ISL6186 turn-on

and turn-off waveforms.

External current loading in excess of the trip current level for the

particular part being evaluated will result in the ISL6186 entering

current limiting mode. Figure 11 illustrates current limiting mode

for the ISL6186 product variants with 1.5A of continuous load

current rating. The scope shot shows current limiting for ~12ms

before it is turned off and the fault signal is asserted.

Application Considerations

See Table 2 for a listing of the ISL6186XEVAL1Z board

components.

Decoupling V

IN

Application considerations for the ISL6186 family are widely

accepted best industry practices. Good decoupling practices on

the V

IN

pin must be followed by placement close to the IC, with at

least 2.2礔 being recommended. For the 3.0 and 3.6A versions,

at least 33礔 is recommended to prevent spiking and glitching

on V

IN

during an OC event. Use good PCB layout practices to

reduce input and output inductance to the ISL6186.

Loading V

OUT

When designing with the 3A and 3.6A versions in an

implementation in which the output may be unloaded (open)

while the ISL6186 is turned on, a minimum of 4.7礔 of

capacitive loading is recommended to prevent high dv/dt from

unnecessarily activating the surge/ESD circuitry.

Continuous Current Ratings

The ISL6186 provides several continuous current rated devices

specified at V

IN

= 5V: these are the 1.5A, 3A and 3.6A options,

which are capable over the entire temperature extreme. At

V

IN

=3.3V, current capability is degraded, and the ISL6186 is

specified at 1.5A and 3A. At V

IN

= 2.5V, there are no

specifications, but a typical value is provided in the specification

table as guidance for +25癈 operation. This degraded capability

is due to the higher r

DS(ON)

of the FET switch at the lower bias

voltage.

Enhanced thermal characteristics and an increased number of

bond wires allows the 10 Ld DFN to have a higher current

capability than either the 8 Ld SOIC or 8 Ld DFN.

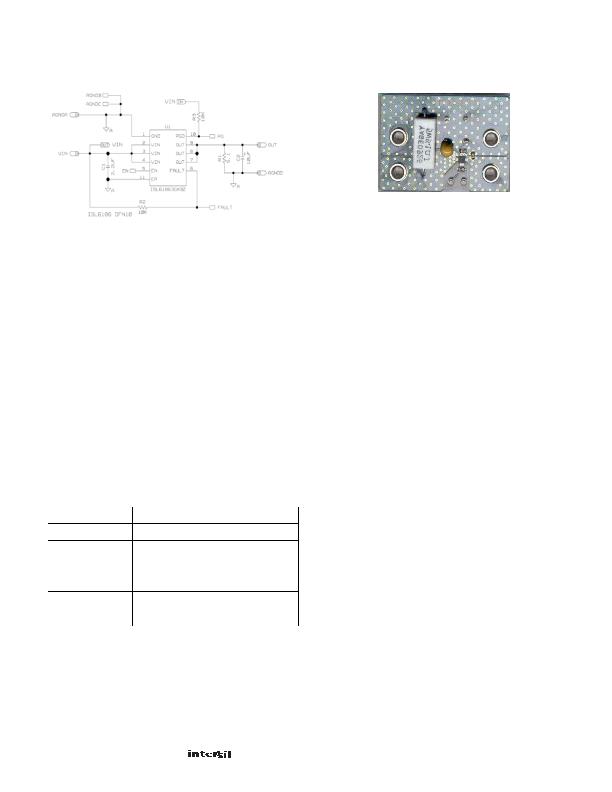

ISL61863EVAL1Z Schematic and Photo

FIGURE 28A. ISL61863EVAL1Z SCHEMATIC

FIGURE 28B. ISL61863EVAL1Z BOARD PHOTO

FIGURE 28. ISL61863EVAL1Z SCHEMATIC and ISL61863EVAL1Z PHOTOGRAPH

*

NOTE: *PGD Output only available on ISL61863 types

GND

VIN

GND

OUT

FLT

EN

PG

TABLE 1. ISL61863EVAL1Z TEST POINT ASSIGNMENTS

TP NAME

DESCRIPTION

GND

Eval Board and IC Gnd

VIN

Eval Board, IC Bias and Power Input

EN

Enable Switch

OUT

Switch Power Output

PG

Power-Good Output

FLT

Fault Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISL6402IR | IC REG TRPL BCK/LINEAR 28-QFN |

| ISL6413IRZ-TK | IC REG TRPL BCK/LINEAR 24-QFN |

| ISL6432CB-T | IC REG QD BCK/LINEAR 16-SOIC |

| ISL6521CBZS2698 | IC REG QD BCK/LINEAR 16-SOIC |

| ISL6528CBZ-TS2698 | IC REG DL BCK/LINEAR SYNC 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISL61861DCBZ-T | 功能描述:熱插拔功率分布 SINGLE USB HOTSWAP 3A/RETRY 8LD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

| ISL61861DIBZ | 功能描述:熱插拔功率分布 SINGLE USB HOTSWAP 3A/RETRY 8LD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

| ISL61861DIBZ-T | 功能描述:熱插拔功率分布 SINGLE USB HOTSWAP 3A/RETRY 8LD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

| ISL61861ECBZ | 功能描述:熱插拔功率分布 SINGLE USB HOTSWAP W 5A/LATCH 8LD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

| ISL61861ECBZ-T | 功能描述:熱插拔功率分布 SINGLE USB HOTSWAP W 5A/LATCH 8LD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。