- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377579 > IS93C66-3GI (INTEGRATED SILICON SOLUTION INC) 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM PDF資料下載

參數(shù)資料

| 型號: | IS93C66-3GI |

| 廠商: | INTEGRATED SILICON SOLUTION INC |

| 元件分類: | DRAM |

| 英文描述: | 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| 中文描述: | 256 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

| 封裝: | SO-8 |

| 文件頁數(shù): | 1/10頁 |

| 文件大小: | 83K |

| 代理商: | IS93C66-3GI |

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. G

04/26/01

1

ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any

errors which may appear in this publication. Copyright 2001, Integrated Silicon Solution, Inc.

IS93C66-3

4,096-BIT SERIAL ELECTRICALLY

ERASABLE PROM

ISSI

OVERVIEW

The IS93C66-3 is a low cost 4,096-bit, non-volatile, serial

E

2

PROM. It is fabricated using ISSI's advanced CMOS

E

2

PROM technology. The IS93C66-3 provides efficient

non-volatile read/write memory arranged as 256 registers

of 16 bits each. Seven 11-bit instructions control the

operation of the device, which includes read, write, and

mode enable functions. The data out pin (D

OUT

) indicates

the status of the device during in the self-timed non-volatile

programming cycle.

The self-timed write cycle includes an automatic erase-

before-write capability. To protect against inadvertent

writes, the WRITE instruction is accepted only while the

chip is in the write enabled state. Data is written in 16 bits

per write instruction into the selected register. If Chip

Select

(CS)

is brought

HIGH

after initiation of the write cycle,

the Data Output (D

OUT

) pin will indicate the

READY/

BUSY

status of the chip.

APPLICATIONS

The IS93C66-3 is ideal for high-volume applications

requiring low power and low density storage. This device

uses a low cost, space saving 8-pin package. Candidate

applications include robotics, alarm devices, electronic

locks, meters and instrumentation settings.

MARCH 2001

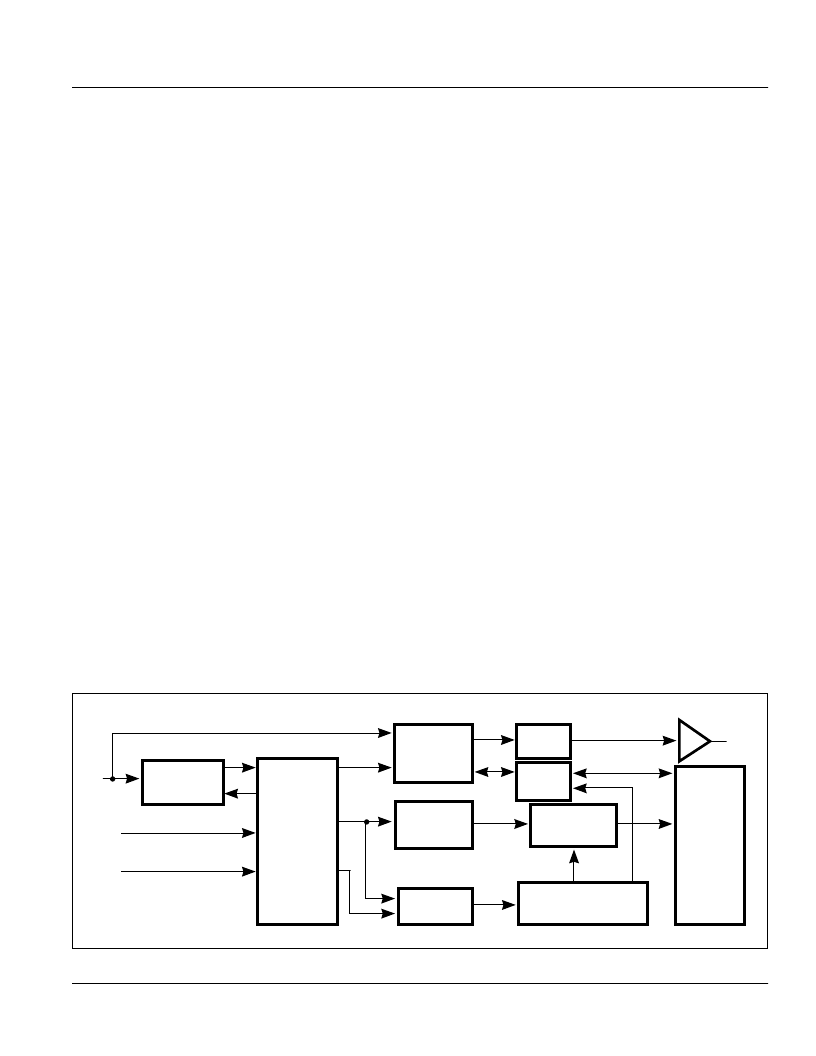

FUNCTIONAL BLOCK DIAGRAM

FEATURES

State-of-the-art architecture

— Non-volatile data storage

— Low voltage operation:

3.0V (Vcc = 2.7V to 6.0V)

— Full TTL compatible inputs and outputs

— Auto increment for efficient data dump

Low voltage read operation

— Down to 2.7V

Hardware and software write protection

— Defaults to write-disabled state at power-up

— Software instructions for write-enable/disable

Advanced low voltage CMOS E

2

PROM

technology

Versatile, easy-to-use interface

— Self-timed programming cycle

— Automatic erase-before-write

— Programming status indicator

— Word and chip erasable

— Stop SK anytime for power savings

Durable and reliable

— 10-year data retention after 100K write cycles

— 100,000 write cycles

— Unlimited read cycles

CS

SK

D

IN

D

OUT

DUMMY

BIT

R/W

AMPS

DATA

REGISTER

(16 BITS)

ADDRESS

REGISTER

1 OF 256

DECODER

WRITE

ENABLE

HIGH VOLTAGE

GENERATOR

INSTRUCTION

DECODE,

CONTROL,

AND

CLOCK

GENERATION

INSTRUCTION

REGISTER

(11 BITS)

EEPROM

ARRAY

(256 X 16)

相關PDF資料 |

PDF描述 |

|---|---|

| IS93C66-3GR | 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3GRI | 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3P | 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3PI | 4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3 | 4,096-Bit Serial EEPROM(4KB串行EEPROM) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IS93C66-3GR | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3GRI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3P | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66-3PI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:4,096-BIT SERIAL ELECTRICALLY ERASABLE PROM |

| IS93C66A | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:2K-BIT/4K-BIT SERIAL ELECTRICALLY ERASABLE PROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。