- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377550 > IS42S16400-10T (INTEGRATED SILICON SOLUTION INC) 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | IS42S16400-10T |

| 廠商: | INTEGRATED SILICON SOLUTION INC |

| 元件分類: | DRAM |

| 英文描述: | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 4M X 16 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| 封裝: | 0.400 INCH, TSOP2-54 |

| 文件頁數(shù): | 21/54頁 |

| 文件大小: | 580K |

| 代理商: | IS42S16400-10T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

IS42S16400

ISSI

Integrated Silicon Solution, Inc.

—

1-800-379-4774

TARGET SPECIFICATION

Rev. C

05/04/01

21

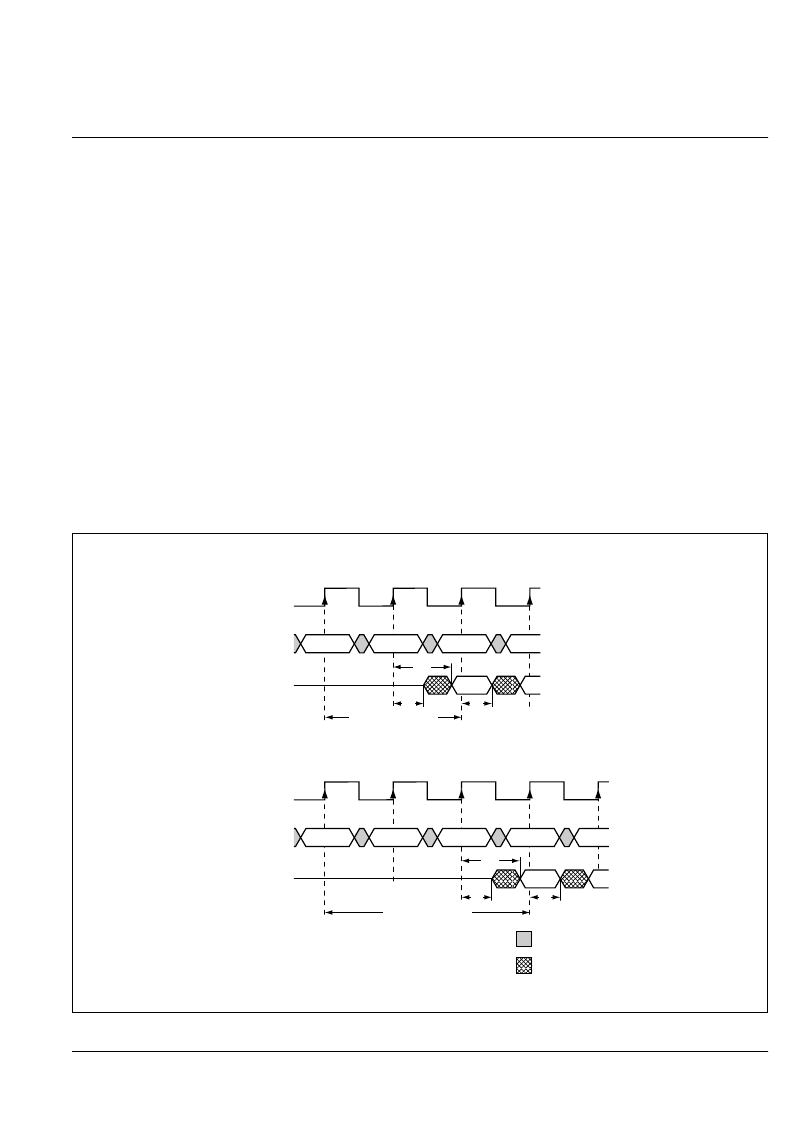

DON'T CARE

UNDEFINED

CLK

COMMAND

DQ

READ

NOP

NOP

NOP

CAS Latency - 3

t

AC

t

OH

D

OUT

T0

T1

T2

T3

T4

t

LZ

CLK

COMMAND

DQ

READ

NOP

NOP

CAS Latency - 2

t

AC

t

OH

D

OUT

T0

T1

T2

T3

t

LZ

CAS Latency

same bank. The PRECHARGE command should be issued

x

cycles before the clock edge at which the last desired

data element is valid, where

x

equals the CAS latency

minus one. This is shown in the READ to PRECHARGE

diagram for each possible CAS latency; data element

n

+

3 is either the last of a burst of four or the last desired of a

longer burst. Following the PRECHARGE command, a

subsequent command to the same bank cannot be issued

until t

RP

is met. Note that part of the row precharge time is

hidden during the access of the last data element(s).

In the case of a fixed-length burst being executed to

completion, a PRECHARGE command issued at the

optimum time (as described above) provides the same

operation that would result from the same fixed-length

burst with auto precharge. The disadvantage of the

PRECHARGE command is that it requires that the com-

mand and address buses be available at the appropriate

time to issue the command; the advantage of the

PRECHARGE command is that it can be used to truncate

fixed-length or full-page bursts.

Full-page READ bursts can be truncated with the BURST

TERMINATE command, and fixed-length READ bursts

may be truncated with a BURST TERMINATE command,

provided that auto precharge was not activated. The

BURST TERMINATE command should be issued

x

cycles

before the clock edge at which the last desired data

element is valid, where

x

equals the CAS latency minus

one. This is shown in the READ Burst Termination

diagram for each possible CAS latency; data element

n

+

3 is the last desired data element of a longer burst.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS42S16400-10TI | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-6T | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-7T | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-7TI | 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16800A1 | 8Meg x16 128-MBIT SYNCHRONOUS DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS42S16400-10TI | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-6T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-7T | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42S16400-7TI | 制造商:Integrated Silicon Solution Inc 功能描述: |

| IS42S16400A | 制造商:ISSI 制造商全稱:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。