- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377488 > IDT82V3002A (Integrated Device Technology, Inc.) WAN PLL WITH DUAL REFERENCE INPUTS PDF資料下載

參數(shù)資料

| 型號: | IDT82V3002A |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | WAN PLL WITH DUAL REFERENCE INPUTS |

| 中文描述: | 廣域網(wǎng)鎖相環(huán)雙基準(zhǔn)輸入 |

| 文件頁數(shù): | 15/28頁 |

| 文件大小: | 390K |

| 代理商: | IDT82V3002A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

15

IDT82V3002A WAN PLL WITH DUAL REFERENCE INPUTS INDUSTRIAL TEMPERATURE RANGE

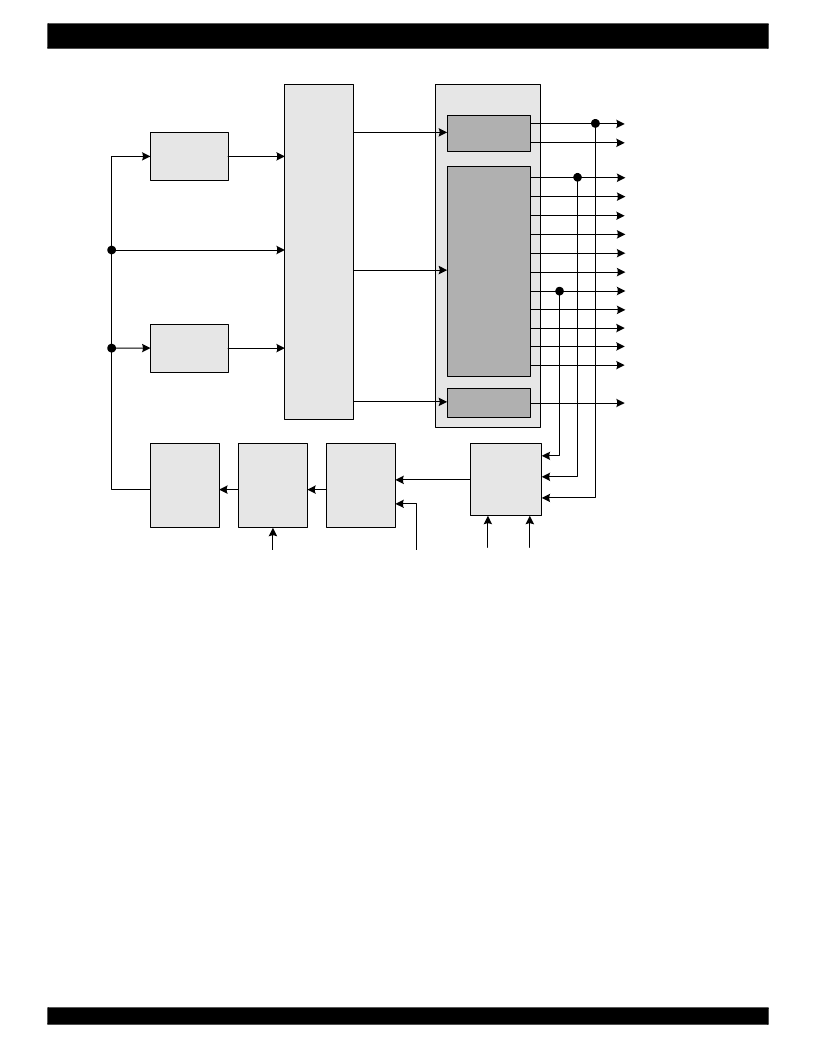

Figure - 8 DPLL Block Diagram

3.7.1

PHASE DETECTOR (PHD)

In Normal Mode, the Phase Detector compares the virtual reference

signal from the TIE Control Circuit with the feedback signal from the

Frequency Select Circuit, and outputs an error signal corresponding to

the phase difference between the two. This error signal is then sent to

the Limiter circuit for phase slope control.

The feedback signal can be 8 kHz, 2.048 MHz or 1.544 MHz, as

selected by F_sel1 and F_sel0 pins. Refer to

Table - 3

for details.

In Freerun or Holdover Mode, the Frequency Select Circuit, the

Phase Detector and the Limiter are not active and the input reference

signals are not used.

3.7.2

LIMITER

The Limiter is used to ensure that the DPLL responds to all input

transient conditions with a maximum output phase slope of 5 ns per 125

μs. This well meets AT&T TR62411 and Telcordia GR-1244-CORE

specifications, which specify the maximum phase slope of 7.6 ns per

125 μs and 81 ns per 1.326 ms respectively.

In Normal Mode, the Limiter receives the error signal from the Phase

Detector, limits the phase slope within 5 ns per 125 μs and sends the

limited signal to the Loop Filter.

The fast lock mode is a submode of Normal Mode. By setting the

FLOCK pin to high, the device will enter fast lock mode. In this mode,

the Limiter is disabled and the DPLL will lock to the incoming reference

within 500 ms.

3.7.3

LOOP FILTER

The Loop Filter ensures that the jitter transfer meets ETS 300 011

and AT&T TR62411 requirements. This Loop Filter works similarly to a

first order low pass filter with 2.1 Hz cutoff frequency for the three valid

input reference signals (8 kHz, 2.048 MHz or 1.544 MHz).

The output of the Loop Filter goes to the Digital Control Oscillator

directly or via the Fraction blocks, in which E1, T1 and C6 signals are

generated.

3.7.4

FRACTION BLOCK

By applying some algorithms to the incoming E1 signal, the

Fraction_C6 and Fraction_T1 blocks generate C6 and T1 signals

respectively.

3.7.5

DIGITAL CONTROL OSCILLATOR (DCO)

In Normal Mode, the DCO receives three limited and filtered signals

from Loop Filter or Fraction blocks. Based on the received signals, the

DCO generates three digital outputs, 25.248 MHz, 32.768 MHz and

D

C32o

F0o

F8o

F16o

F32o

C16o

C8o

C4o

C2o

C3o

C6o

RSP

TSP

C1.5o

Output Interface

T1_Divider

E1_Divider

C6_Divider

Frequency

Selection

Circuit

Phase

Detector

Virtual Reference

Loop Filter

Fraction_C6

Fraction_T1

24.704 MHz

32.768 MHz

25.248 MHz

Feedback

Signal

Limiter

FLOCK

F_sel1 F_sel0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT82V3002APV | WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3010 | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PVG | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3255 | WAN PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT82V3002A_08 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3002A-01PVG | 功能描述:IC PLL WAN T1/E1 56SSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標(biāo)準(zhǔn)包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應(yīng)商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

| IDT82V3002A-01PVG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN T1/E1 56SSOP |

| IDT82V3002APV | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3002APVG | 功能描述:IC PLL WAN T1/E1 DUAL REF 56SSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標(biāo)準(zhǔn)包裝:1,500 系列:- 類型:時鐘緩沖器/驅(qū)動器 PLL:是 主要目的:- 輸入:- 輸出:- 電路數(shù):- 比率 - 輸入:輸出:- 差分 - 輸入:輸出:- 頻率 - 最大:- 電源電壓:3.3V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應(yīng)商設(shè)備封裝:28-SSOP 包裝:帶卷 (TR) 其它名稱:93786AFT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。