- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377486 > IDT7MPV6253S15M (INTEGRATED DEVICE TECHNOLOGY INC) 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO PDF資料下載

參數(shù)資料

| 型號: | IDT7MPV6253S15M |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| 中文描述: | 32K X 64 CACHE TAG SRAM MODULE, 15 ns, DMA178 |

| 封裝: | CELP MODULE-178 |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 84K |

| 代理商: | IDT7MPV6253S15M |

IDT7MPV6253/55/56

256KB/512KB CMOS SECONDARY CACHE MODULES FOR THE PowerPC

COMMERCIAL TEMPERATURE RANGE

2

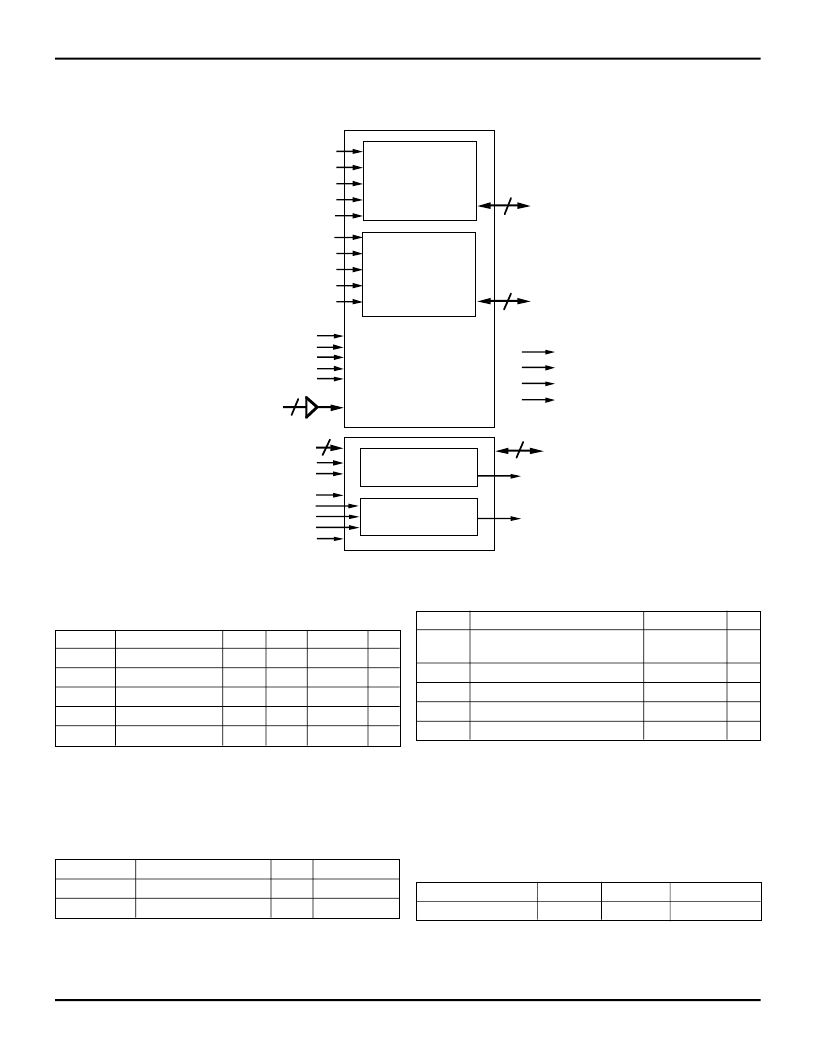

FUNCTIONAL BLOCK DIAGRAM

IDT7MPV6255 – 256KB PIPELINED BURST VERSION

32K x 32

Pipelined

Burst

SRAM

WE#

0

WE#

1

WE#

2

WE#

3

CLK

1

WE#

4

WE#

5

WE#

6

WE#

7

32K x 32

Pipelined

Burst

SRAM

CLK

0

PD

2

PD

3

PD

0

PD

1

8K x 12

Tag Field

A

14

- A

2613

TWE#

TOE#

A

2

- A

13

12

8K x 2

Status

STANDBY

TCLR#

TVALID

DIRTYIN

CLK

2

TMATCH

DIRTYOUT

SRAM OE#0

SRAM ADS#0

CNT EN#0

STANDBY

BURST MODE

A

14

- A

28

15

DH

0

-

31

32

DL

0

-

31

32

drw 02

RECOMMENDED DC

OPERATING CONDITIONS

Symbol

V

CC3

V

CC5

GND

V

IH

V

IL

Parameter

Supply Voltage

Supply Voltage

Supply Voltage

Input High Voltage

Input Low Voltage

Min.

3.14

4.75

0

2.2

–0.5

(1)

Typ.

3.3

5.0

0

—

—

Max.

3.6

5.25

0.0

V

CC

+ 0.3

0.8

Unit

V

V

V

V

V

NOTE:

1. V

IL

= –1.0V for pulse width less than 5ns, once per cycle.

tbl 01

ABSOLUTE MAXIMUM RATINGS

Symbol

V

TERM

for V

CC3

to GND

T

A

T

BIAS

T

STG

I

OUT

NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other conditions above those

indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may

affect reliability.

Rating

Value

Unit

V

Terminal Voltage with Respect

–0.5 to +4.6

Operating Temperature

Temperature Under Bias

Storage Temperature

DC Output Current

0 to +70

–10 to +85

–55 to +125

50

°

C

°

C

°

C

mA

tbl 03

RECOMMENDED OPERATING

TEMPERATURE AND SUPPLY VOLTAGE

Power Plane

V

CC3

V

CC5

Ambient Temperature

0

°

C to +70

°

C

0

°

C to +70

°

C

GND

0V

0V

V

CC

3.3V +10/-5%

5.0V

±

5%

tbl 02

SRAM ACCESS TIMES

Module Speed

66MHz

Asych

15ns

Burst

(1)

8.5ns

Tag

10ns

NOTE:

1. Burst SRAMs are measured by Clock to Data Out (t

CD

).

tbl 04

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7MPV6253S66M | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6255S15M | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6255S66M | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6253 | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6255 | Octal Bus Transceivers with 3-State Outputs 20-TSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT80ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT80HCPS1432CHM | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CHMI | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CRM | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CRMI | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。