- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377486 > IDT7MPV6253S66M (Integrated Device Technology, Inc.) 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO PDF資料下載

參數(shù)資料

| 型號: | IDT7MPV6253S66M |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| 中文描述: | 256KB和512KB的庫PowerPCO二級緩存模塊 |

| 文件頁數(shù): | 1/7頁 |

| 文件大?。?/td> | 84K |

| 代理商: | IDT7MPV6253S66M |

Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE

JUNE 1996

1996 Integrated Device Technology, Inc.

DSC-3608/2

1

FEATURES

For CHRP based PowerPC

systems.

Asynchronous and pipelined burst SRAM options in the

same module pinout

Low-cost, low-profile card edge module with 178 leads

Uses Burndy Computerbus

connector, part number

ELF182KSC-3Z50

Operates with external PowerPC CPU speeds up to

66MHz

Separate 5V (

±

5%) and 3.3V (+10/-5%) power supplies

Multiple GND pins and decoupling capacitors for maxi-

mum noise immunity

Presence Detect output pins allow the system to deter-

mine the particular cache configuration.

DESCRIPTION

The IDT7MPV6253/55/56 modules belong to a family of

secondary caches intended for use with PowerPC CPU-

based systems. The IDT7MPV6253 uses IDT’s 71V256 32K

The IDT logo is a registered trademark of Integrated Device Technology, Inc. PowerPC is a trademark of IBM. Computerbus is trademark of Burndy.

x 8 asynchronous static RAMs and the IDT7MPV6255/56 use

IDT’s 71V432 32K x 32 pipelined synchronous burst static

RAMs in plastic surface mount packages mounted on a

multilayer epoxy laminate (FR-4) board. In addition, each of

the modules uses the IDT 71216 16K x 15 Cache-Tag static

RAM and IDT FCT logic. Extremely high speeds are achieved

using IDT’s high-reliability, low cost CMOS technology.

The low profile card edge package allows 178 signal leads

to be placed on a package 5.06" long, a maximum of 0.250"

thick and a maximum of 1.08" tall. The module space savings

versus discrete components allows the OEM to design addi-

tional functions onto the system or to shrink the size of the

motherboard for reduced cost.

All inputs and outputs are LVTTL-compatible, and operate

from separate 5V (

±

5%) and 3.3V (+10/-5%) power supplies.

Multiple GND pins and on-board decoupling capacitors en-

sure maximum protection from noise.

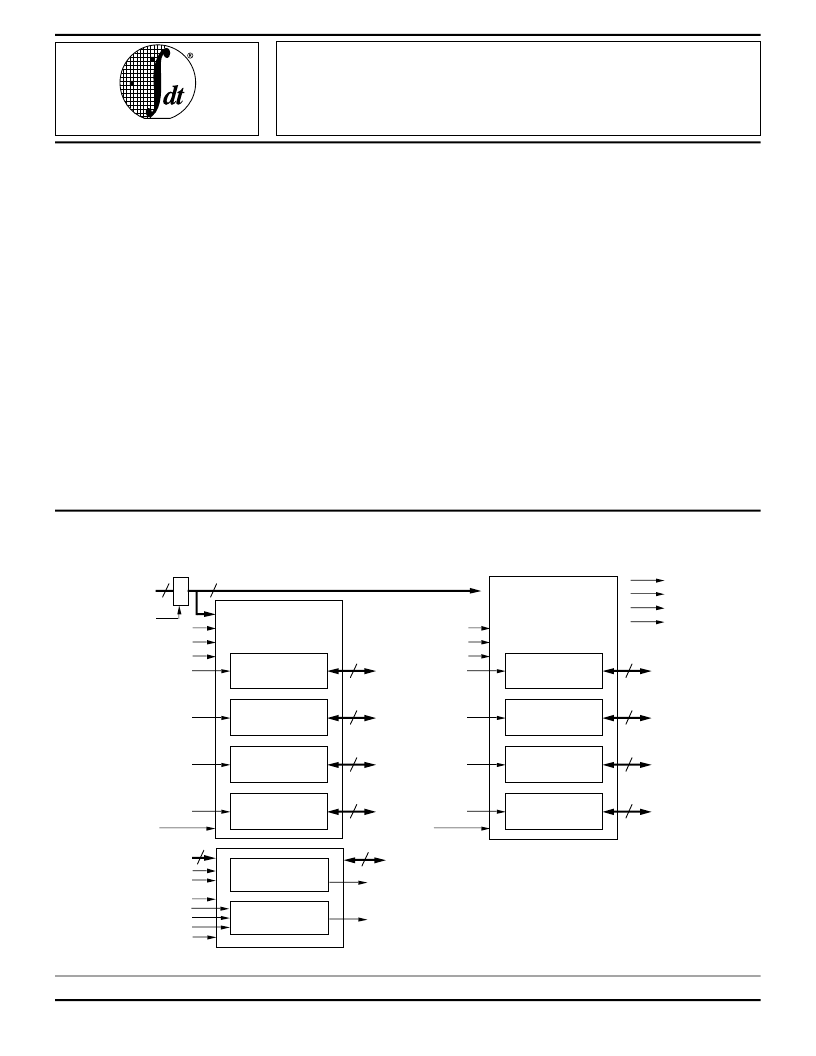

FUNCTIONAL BLOCK DIAGRAM

IDT7MPV6253 – 256KB ASYNCHRONOUS VERSION

drw 01

DH

0

- DH

7

DH

8

- DH

15

DH

16

- DH

23

DH

24

- DH

31

8

8

8

8

WE#

0

WE#

1

WE#

2

WE#

3

SRAM OE

1

DL

0

- DL

7

DL

8

- DL

15

DL

16

- DL

23

DL

24

- DL

31

WE#

4

WE#

5

WE#

6

WE#

7

ADDR

A0

ADDR

A1

A

14

- A

26

PD

2

PD

3

PD

0

PD

1

L

ADDR

A0

ADDR

A1

SRAM OE

0

13

13

8K x 12

Tag Field

32K x 8

Asynchronous

SRAM

A

14

- A

2613

TWE#

TOE#

ALE

32K x 8

Asynchronous

SRAM

8

8

8

8

32K x 8

Asynchronous

SRAM

32K x 8

Asynchronous

SRAM

32K x 8

Asynchronous

SRAM

32K x 8

Asynchronous

SRAM

32K x 8

Asynchronous

SRAM

32K x 8

Asynchronous

SRAM

A

2

- A

13

12

8K x 2

Status

STANDBY

TCLR#

TVALID

DIRTYIN

CLK

2

TMATCH

DIRTYOUT

STANDBY

STANDBY

256KB AND 512KB SECONDARY

CACHE MODULES FOR THE

PowerPC

IDT7MPV6253

IDT7MPV6255/56

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7MPV6255S15M | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6255S66M | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6253 | 256KB AND 512KB SECONDARY CACHE MODULES FOR THE PowerPCO |

| IDT7MPV6255 | Octal Bus Transceivers with 3-State Outputs 20-TSSOP -40 to 85 |

| IDT7MPV6256 | Octal Bus Transceivers with 3-State Outputs 20-TSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT80ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT80HCPS1432CHM | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CHMI | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CRM | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

| IDT80HCPS1432CRMI | 制造商:Integrated Device Technology Inc 功能描述:IC RIO SWITCH GEN2 576FCBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。