- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4019 > IDT79RC64T575-200DP (IDT, Integrated Device Technology Inc)IC MPU 64BIT EMB 200MHZ 208-QFP PDF資料下載

參數(shù)資料

| 型號: | IDT79RC64T575-200DP |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 23/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC MPU 64BIT EMB 200MHZ 208-QFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 處理器類型: | RISC 64-位 |

| 速度: | 200MHz |

| 電壓: | 2.5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 包裝: | 托盤 |

| 其它名稱: | 79RC64T575-200DP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁

4 of 28

December 14, 2001

79RC64574 79RC64575

ferring data between the processor and memory at a peak rate of

1000MB/sec. A boot-time selectable option to run the system interface

as 32-bits wide—using basically the same protocols as the 64-bit

system—is also supported.

A boot-time mode control interface initializes fundamental

processor modes and is a serial interface that operates at a very low

frequency (SysClock divided by 256). This low-frequency operation

allows the initialization information to be kept in a low-cost EPROM;

alternatively, the twenty-or-so bits could be generated by the system

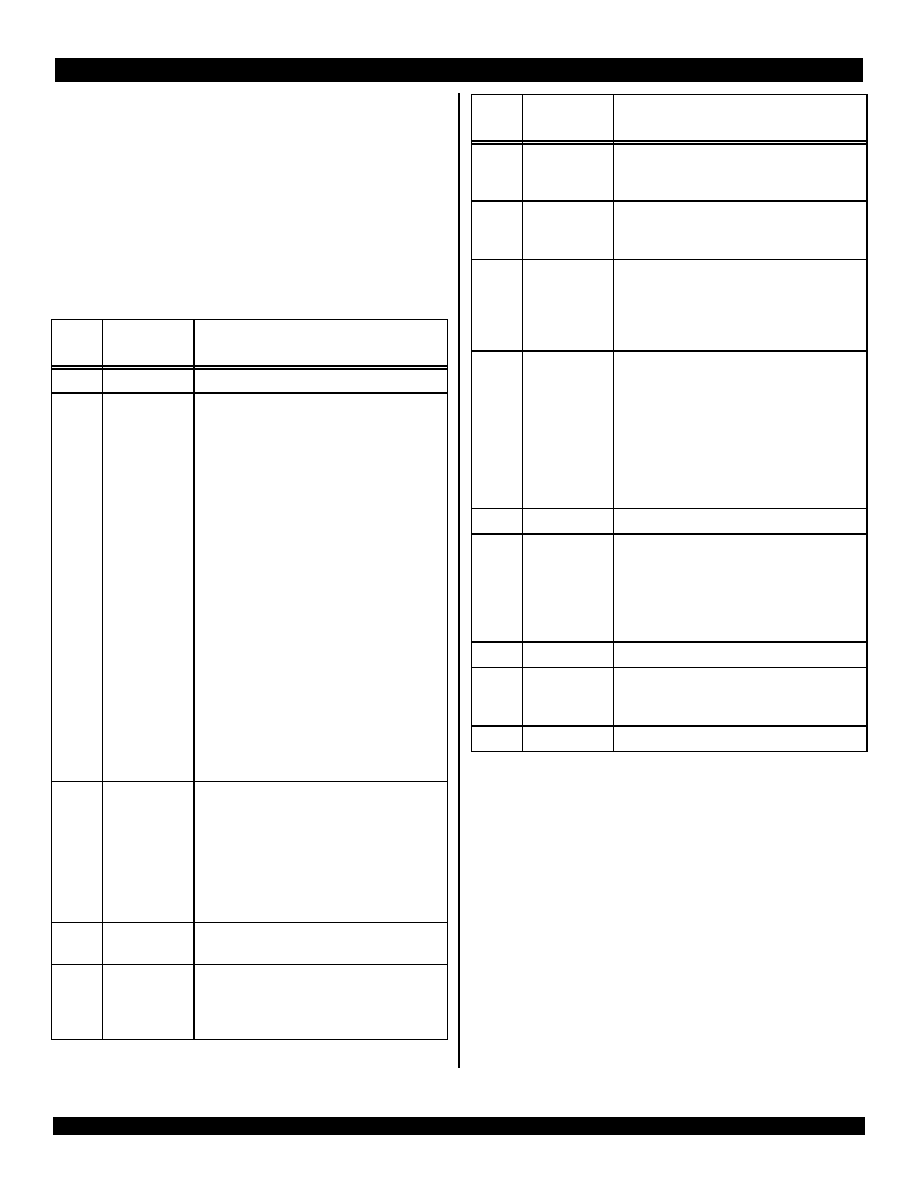

interface ASIC or a simple PAL. The boot-time serial stream is shown in

Serial

Bit Description

Value & Mode Setting

0

Reserved

Must be set to 0.

1:4

Transmit-data-

pattern.

Bit 4 is MSB

64-bit bus width:

0: DDDD

1: DDxDDx

2: DDxxDDxx

3: DxDxDxDx

4: DDxxxDDxxx

5: DDxxxxDDxxxx

6: DxxDxxDxxDxx

7: DDxxxxxxDDxxxxxx

8: DxxxDxxxDxxxDxxx

9-15: Reserved. Must not be selected.

32-bit bus width:

0: WWWWWWWW

1: WWxWWxWWxWWx

2: WWxxWWxxWWxxWWxx

3: WxWxWxWxWxWxWxWx

4: WWxxxWWxxxWWxxxWWxxx

5: WWxxxxWWxxxxWWxxxxWWxxxx

6: WxxWxxWxxWxxWxxWxxWxxWxx

7: WWxxxxxxWWxxxxxxWWxxxxxxWWxxxxxx

8: WxxxWxxxWxxxWxxxWxxxWxxxWxxxWxxx

9-15: Reserved. Must not be selected.

5:7

PClock-to-

SysClk-Ratio.

Bit 7 is MSB

0: 2

1: 3

2: 4

3: 5

4: 6

5: 7

6: 8

7: Reserved

8

Endianness

0: Little endian

1: Big endian

9:10

Non-block write

Mode. Bit 10 is

MSB

00: R4400 compatible

01: Reserved

10: Pipelined-Write-Mode

11: Write-Reissue-Mode

Table 3 Boot-time Mode Stream (Page 1 of 2)

The clocking interface allows the CPU to be easily mated with

external reference clocks. The CPU input clock is the bus reference

clock and can be between 33 and 125MHz. An on-chip phase-locked-

loop (PLL) generates the pipeline clock (PClock) through multiplication

of the system interface clock by values of 2,3,4,5,6,7 or 8, as defined at

system reset. This allows the pipeline clock to be implemented at a

significantly higher frequency than the system interface clock. The

RC64574/575 support both single data (one byte through full CPU bus

width) and 8-word block transfers on the SysAD bus.

The RC64574/575 implement additional write protocols that

double the effective write bandwidth. The write re-issue has a repeat

rate of 2 cycles per write. Pipelined writes have the same 2-cycle per

write repeat rate, but can issue an additional write after WrRdy* de-

asserts.

11

TimerIntEn

Timer interrupt settings:

0: Enable Timer Interrupt on Int(5)

1: Disable Timer Interrupt on Int(5)

12

System Interface

Bus Width.

Interface bus width control settings:

0: 64-bit system interface

1: 32-bit system interface

13:14

Drv_Out

Bit 14 is MSB

Slew rate control of the output drivers:

10: 100% strength (fastest)

11: 83% strength

00: 67% strength

01: 50% strength (slowest)

15:17

Write address to

write data delay.

From 0 to 7 SysClk cycles:

0: AD...

1: AxD...

2: AxxD...

3: AxxxD...

4: AxxxxD...

5: AxxxxxD...

6: AxxxxxxD...

7: AxxxxxxxD...

18

Reserved

User must select ‘0’

19

Extend

Multiplication

Repeat Rate.

Initial setting of the “Fast Multiply” bit.

0: Enable Fast Multiply

1: Do not Enable Fast Multiply

Note: For pipeline speeds >250MHz, this bit must

be set to ‘1’.

20:24

Reserved

User must select ‘0’

25:26

System

configuration

identifier.

Software visible in processorConfig[21:20]

0: Config[21:20] = Mode Bit [25:26]

Must be set to 0.

27:256

Reserved

User must select ‘0’

Serial

Bit Description

Value & Mode Setting

Table 3 Boot-time Mode Stream (Page 2 of 2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMC40DTEH | CONN EDGECARD 80POS .100 EYELET |

| FMC40DRAS-S734 | CONN EDGECARD 80POS .100 R/A SLD |

| RSC65DTEN | CONN EDGECARD 130POS .100 EYELET |

| RSC65DTEH | CONN EDGECARD 130POS .100 EYELET |

| EMC40DTES | CONN EDGECARD 80POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT79RC64T575-250DP | 功能描述:IC MPU 64BIT EMB 250MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC64V474-180DZ | 功能描述:IC MPU 64BIT EMB 180MHZ 128-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC64V474-200DZ | 功能描述:IC MPU 64BIT EMB 200MHZ 128-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC64V475-180DP | 功能描述:IC MPU 64BIT EMB 180MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC64V475-200DP | 功能描述:IC MPU 64BIT EMB 200MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。