- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4583 > IDT72V51436L7-5BB8 (IDT, Integrated Device Technology Inc)IC FLOW CTRL MULTI QUEUE 256-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V51436L7-5BB8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 55/57頁 |

| 文件大小: | 0K |

| 描述: | IC FLOW CTRL MULTI QUEUE 256-BGA |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類型: | 多隊(duì)列流量控制 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 256-BBGA |

| 供應(yīng)商設(shè)備封裝: | 256-BGA(17x17) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V51436L7-5BB8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁

7

IDT72V51436/72V51446/72V51456 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES

(16 QUEUES) 36 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

BM

BusMatching

LVTTL

This pin is setup before Master Reset and must not toggle during any device operation. This pin is used

INPUT

along with IW and OW to setup the multi-queue flow-control device bus width. Please refer to Table 3

fordetails.

D[35:0]

Data Input Bus

LVTTL

These are the 36 data input pins. Data is written into the device via these input pins on the rising edge

Din

INPUT

ofWCLKprovidedthat

WENisLOW.Note,thatinPacketmodeD32-D35maybeusedaspacketmarkers,

please see packet ready functional discussion for more detail. Due to bus matching not all inputs may be

used, any unused inputs should be tied LOW.

DF(1)

Default Flag

LVTTL

If the user requires default programming of the multi-queue device, this pin must be setup before Master

INPUT

Reset and must not toggle during any device operation. The state of this input at master reset determines

the value of the

PAE/PAF flag offsets. If DF is LOW the value is 8, if DF is HIGH the value is 128.

DFM(1)

Default Mode

LVTTL

The multi-queue device requires programming after master reset. The user can do this serially via the

INPUT

serial port, or the user can use the default method. If DFM is LOW at master reset then serial mode will be

selected, if HIGH then default mode is selected.

ESTR

PAEn Flag Bus

LVTTL

If direct operation of the

PAEn bus has been selected, the ESTR input is used in conjunction with RCLK

Strobe

INPUT

and the RDADD bus to select a sector of queues to be placed on to the

PAEn bus outputs. A sector

addressed via the RDADD bus is selected on the rising edge of RCLK provided that ESTR is HIGH. If

Polled operations has been selected, ESTR should be tied inactive, LOW. Note, that a

PAEn flag bus

selectioncannotbemade,(ESTRmustNOTgoactive)untilprogrammingoftheparthasbeencompleted

and

SENO has gone LOW.

ESYNC

PAEn Bus Sync

LVTTL

ESYNC is an output from the multi-queue device that provides a synchronizing pulse for the

PAEn bus

OUTPUT

duringPolledoperationofthe

PAEnbus.DuringPolledoperationeachsectorofqueuestatusflagsisloaded

on to the

PAEn bus outputs sequentially based on RCLK. The first RCLK rising edge loads sector 1 on

to

PAEn,thesecondRCLKrisingedgeloadssector2.ThethirdRCLKrisingedgewillagainloadsector1.

During the RCLK cycle that sector 1 of a selected device is placed on to the

PAEnbus,theESYNCoutput

will be HIGH. For sector 2 of that device, the ESYNC output will be LOW.

EXI

PAEnBus

LVTTL

The EXI input is used when multi-queue devices are connected in expansion mode and Polled

PAEn

Expansion In

INPUT

bus operation has been selected . EXI of device ‘N’ connects directly to EXO of device ‘N-1’. The EXI

receives a token from the previous device in a chain. In single device mode the EXI input must be tied

LOW if the

PAEnbusisoperatedindirectmode.IfthePAEnbusisoperatedinpolledmodetheEXIinput

must be connected to the EXO output of the same device. In expansion mode the EXI of the first device

should be tied LOW, when direct mode is selected.

EXO

PAEnBus

LVTTL

EXO is an output that is used when multi-queue devices are connected in expansion mode and Polled

Expansion Out

OUTPUT

PAEnbusoperationhasbeenselected.EXOofdevice‘N’connectsdirectlytoEXIofdevice‘N+1’.This

pin pulses when device N has placed its 2nd sector on to the

PAEnbuswithrespecttoRCLK.Thispulse

(token) is then passed on to the next device in the chain ‘N+1’ and on the next RCLK rising edge the first

sector of device N+1 will be loaded on to the

PAEnbus.ThiscontinuesthroughthechainandEXOofthe

last device is then looped back to EXI of the first device. The ESYNC output of each device in the chain

provides synchronization to the user of this looping event.

FF

Full Flag

LVTTL

This pin provides the full flag output for the active queue, that is, the queue selected on the input port for

OUTPUT

write operations, (selected via WCLK, WRADD bus and WADEN). On the WCLK cycle after a queue

selection, this flag will show the status of the newly selected queue. Data can be written to this queue on

the next cycle provided

FF is HIGH. This flag has High-Impedance capability, this is important during

expansionofdevices,whenthe

FFflagoutputofupto8devicesmaybeconnectedtogetheronacommon

line. The device with a queue selected takes control of the

FFbus,allotherdevicesplacetheirFFoutput

into High-Impedance. When a queue selection is made on the write port this output will switch from

High-Impedance control on the next WCLK cycle. This flag is synchronized to WCLK.

FM(1)

Flag Mode

LVTTL

This pin is setup before a master reset and must not toggle during any device operation. The state of the

INPUT

FMpinduringMasterResetwilldeterminewhetherthe

PAFnandPAEnflagbussesoperateineitherPolled

or Direct mode. If this pin is HIGH the mode is Polled, if LOW then it will be Direct.

FSTR

PAFn Flag Bus

LVTTL

If direct operation of the

PAFnbushasbeenselected,theFSTRinputisusedinconjunctionwithWCLK

Strobe

INPUT

and the WRADD bus to select a sector of queues to be placed on to the

PAFn bus outputs. A sector

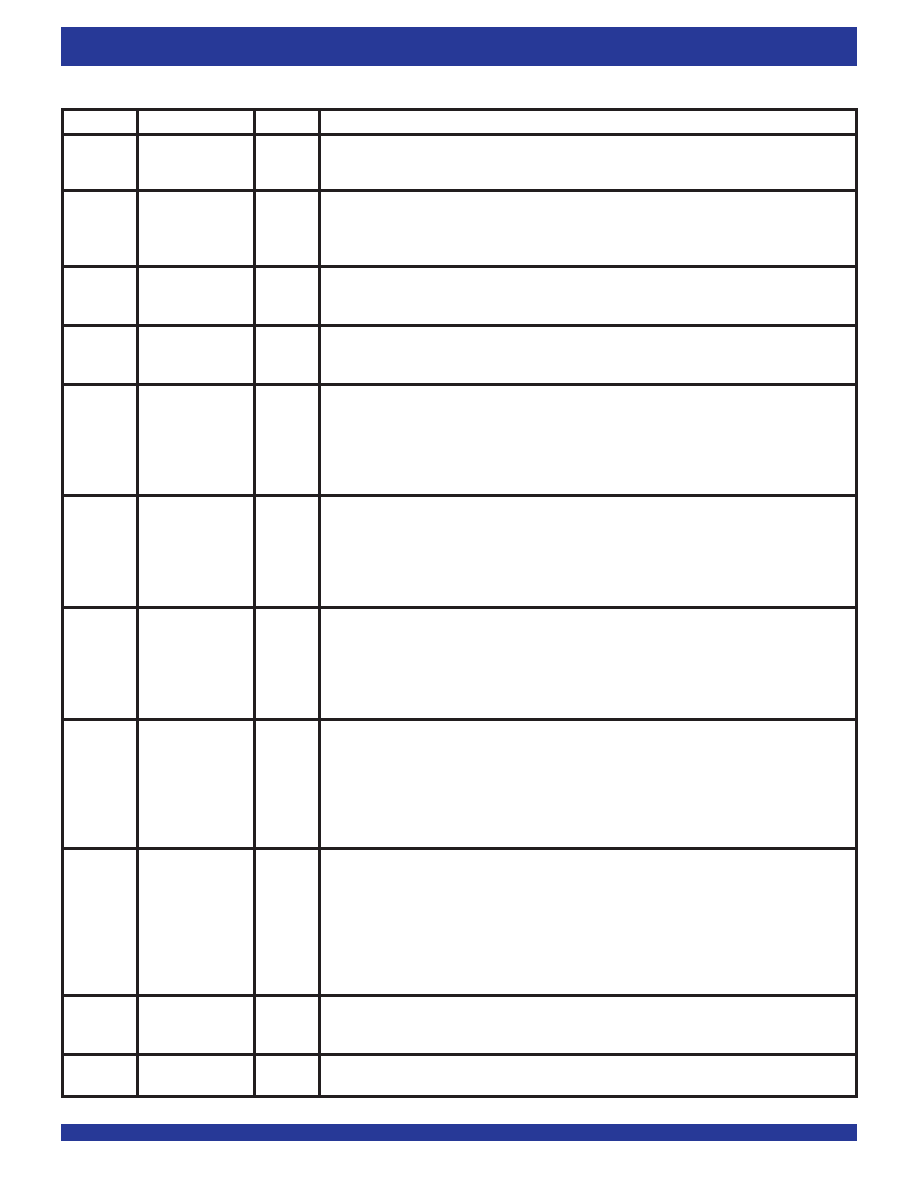

PIN DESCRIPTIONS

Symbol

Name

I/O TYPE

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72V51433L7-5BB8 | IC FLOW CTRL MULTI QUEUE 256-BGA |

| IDT72V51256L7-5BB | IC FLOW CTRL MULTI QUEUE 256-BGA |

| HMC36DRYH | CONN EDGECARD 72POS DIP .100 SLD |

| FMC17DRYS | CONN EDGECARD 34POS DIP .100 SLD |

| ACB65DHRR | CONN CARD EXTEND 130POS .050" |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V51436L7-5BBI | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51443L6BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51443L6BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51443L7-5BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72V51443L7-5BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。