- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377421 > IDT72615L50PF (INTEGRATED DEVICE TECHNOLOGY INC) CMOS SyncBiFIFOO 256 x 18 x 2 and 512 x 18 x 2 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72615L50PF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS SyncBiFIFOO 256 x 18 x 2 and 512 x 18 x 2 |

| 中文描述: | 512 X 18 BI-DIRECTIONAL FIFO, 25 ns, PQFP64 |

| 封裝: | TQFP-64 |

| 文件頁數(shù): | 9/20頁 |

| 文件大小: | 209K |

| 代理商: | IDT72615L50PF |

IDT72605/IDT72615 CMOS SyncBiFIFO

256 x 18 x 2 and 512 x 18 x 2

COMMERCIAL TEMPERATURE RANGE

5.18

9

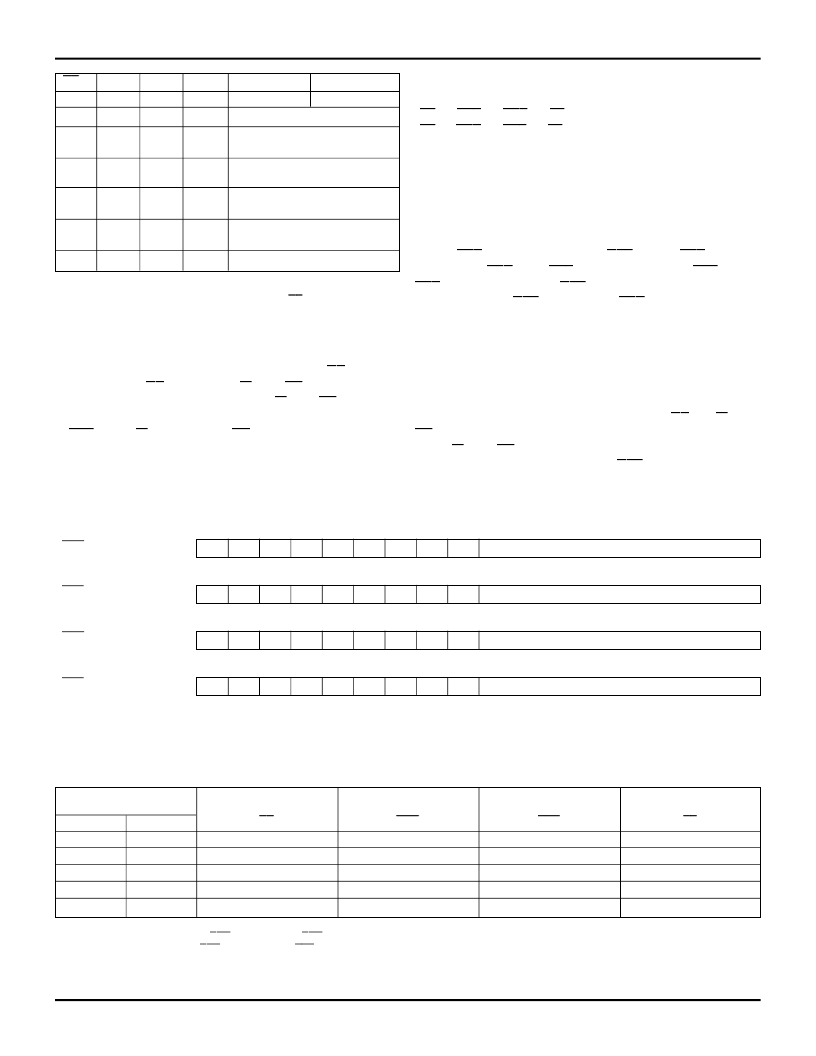

Table 2. Accessing Port A Resources Using

CS

A

, A

2

, A

1

, and A

0.

Number of Words

in FIFO

From

0

1

n+1

D-m

D

To

0

n

EF

LOW

HIGH

HIGH

HIGH

HIGH

PAE

LOW

LOW

HIGH

HIGH

HIGH

PAF

HIGH

HIGH

HIGH

LOW

LOW

FF

HIGH

HIGH

HIGH

HIGH

LOW

D-(m+1)

D-1

D

NOTES:

n = Programmable Empty Offset (

PAE

AB

Register or

PAE

BA

Register)

m = Programmable Full Offset (

PAF

AB

Register or

PAF

BA

Register)

D = FIFO Depth (IDT72605 = 256 words, IDT72615= 512 words)

2704 tbl 12

Table 4. Internal Flag Truth Table.

17

X

16

X

15

X

14

X

13

X

12

X

11

X

10

X

9

X

8

7

A

→

B FIFO Almost-Empty Flag Offset

6

5

4

3

2

1

0

PAE

AB

Register

17

X

16

X

15

X

14

X

13

X

12

X

11

X

10

X

9

X

8

7

6

5

4

3

2

1

0

PAF

AB

Register

A

→

B FIFO Almost-Full Flag Offset

17

X

16

X

15

X

14

X

13

X

12

X

11

X

10

X

9

X

8

7

B

→

A FIFO Almost-Empty Flag Offset

6

5

4

3

2

1

0

PAE

BA

Register

17

X

16

X

15

X

14

X

13

X

12

X

11

X

10

X

9

X

8

7

6

5

4

3

2

1

0

PAF

BA

Register

B

→

A FIFO Almost-Full Flag Offset

NOTE:

1. Bit 8 must be set to 0 for the IDT72605 (256 x 18) Synchronous BiFIFO.

2704 tbl 11

Table 3. Flag Offset Register Format.

PROGRAMMABLE FLAGS

The IDT SyncBiFIFO has eight flags: four flags for A

→

B FIFO

(

EF

AB

,

PAE

AB

,

PAF

AB

,

FF

AB

), and four flags for B

→

A FIFO

(

EF

BA

,

PAE

BA

,

PAF

BA

,

FF

BA

). The Empty and Full flags are

fixed, while the Almost Empty and Almost Full offsets can be

set to any depth through the Flag Offset Registers (see Table

3). The flags are asserted at the depths shown in the Flag

Truth Table (Table 4). After reset, the programmable flag

offsets are set to 8. This means the Almost Empty flags are

asserted at Empty +8 words deep, and the Almost Full flags

are asserted at Full -8 words deep.

The

PAE

AB

is synchronized to

CLK

B

, while

PAE

AB

is syn-

chronized to

CLK

A

; and

PAE

BA

is synchronized to

CLK

A

, while

PAE

BA

is synchronized to

CLK

B

. If the minimum time (t

SKEW2

)

between a rising

CLK

B

and a rising

CLK

A

is met, the flag will

change state on the current clock; otherwise, the flag may not

change state until the next clock rising edge. For the specific

flag timings, refer to Figures 12-15.

PORT B CONTROL SIGNALS

The Port B control signal pins dictate the various operations

shown in Table 5. Port B is independent of

CS

A

. R/

W

B

and

EN

B

lines determine when Data can be written or read in Port

B. If R/

W

B

and

EN

B

are LOW, data is written into input register,

and on LOW-to-HIGH transition of

CLK

B

data is written into

2704 tbl 10

CS

A

0

0

0

A

2

0

0

1

A

1

0

0

0

A

0

0

1

0

Read

Write

A

→

B FIFO

B

→

A FIFO

18-bit Bypass Path

A

→

B FIFO Almost-Empty

Flag Offset

A

→

B FIFO Almost-Full

Flag Offset

B

→

A FIFO Almost-Empty

Flag Offset

B

→

A FIFO Almost-Full

Flag Offset

Port A Disabled

0

1

0

1

0

1

1

0

0

1

1

1

1

X

X

X

PORT A CONTROL SIGNALS

The Port A control signals pins dictate the various opera-

tions shown in Table 2. Port A is accessed when

CS

A

is LOW,

and is inactive if

CS

A

is HIGH. R/

W

A

and

EN

A

lines determine

when Data A can be written or read. If R/

W

A

and

EN

A

are LOW,

data is written into input register on the LOW-to-HIGH transition

of

CLK

A

. If R/

W

A

is HIGH and

OE

A

is LOW, data comes out

of bus and is read from output register into three-state buffer.

Refer to pin descriptions for more information.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72811 | DUAL CMOS SyncFIFO |

| IDT72831L12PF | DUAL CMOS SyncFIFO |

| IDT72831L15PF | DUAL CMOS SyncFIFO |

| IDT72831L25PF | DUAL CMOS SyncFIFO |

| IDT72831L35PF | DUAL CMOS SyncFIFO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72615L50PF8 | 功能描述:IC FIFO BY SYNC 512X18X2 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72801L10PF | 功能描述:IC FIFO SYNC DUAL 256X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72801L10PF8 | 功能描述:IC FIFO SYNC DUAL 256X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72801L10PFG | 功能描述:IC FIFO SYNC DUAL 256X9 64-TQFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72801L10PFG8 | 功能描述:IC FIFO SYNC DUAL 256X9 64-TQFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。