- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄9925 > IDT723676L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 16384X36 128QFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT723676L15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 4/39頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO SYNC 16384X36 128QFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 576K(16K x 36) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問(wèn)時(shí)間: | 15ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 723676L15PF8 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

12

IDT723656/723666/723676 CMOS TRIPLE BUS SyncFIFOTM WITH

BUS MATCHING 2,048 x 36 x 2, 4,096 x 36 x 2 and 8,192 x 36 x 2

COMMERCIALTEMPERATURERANGE

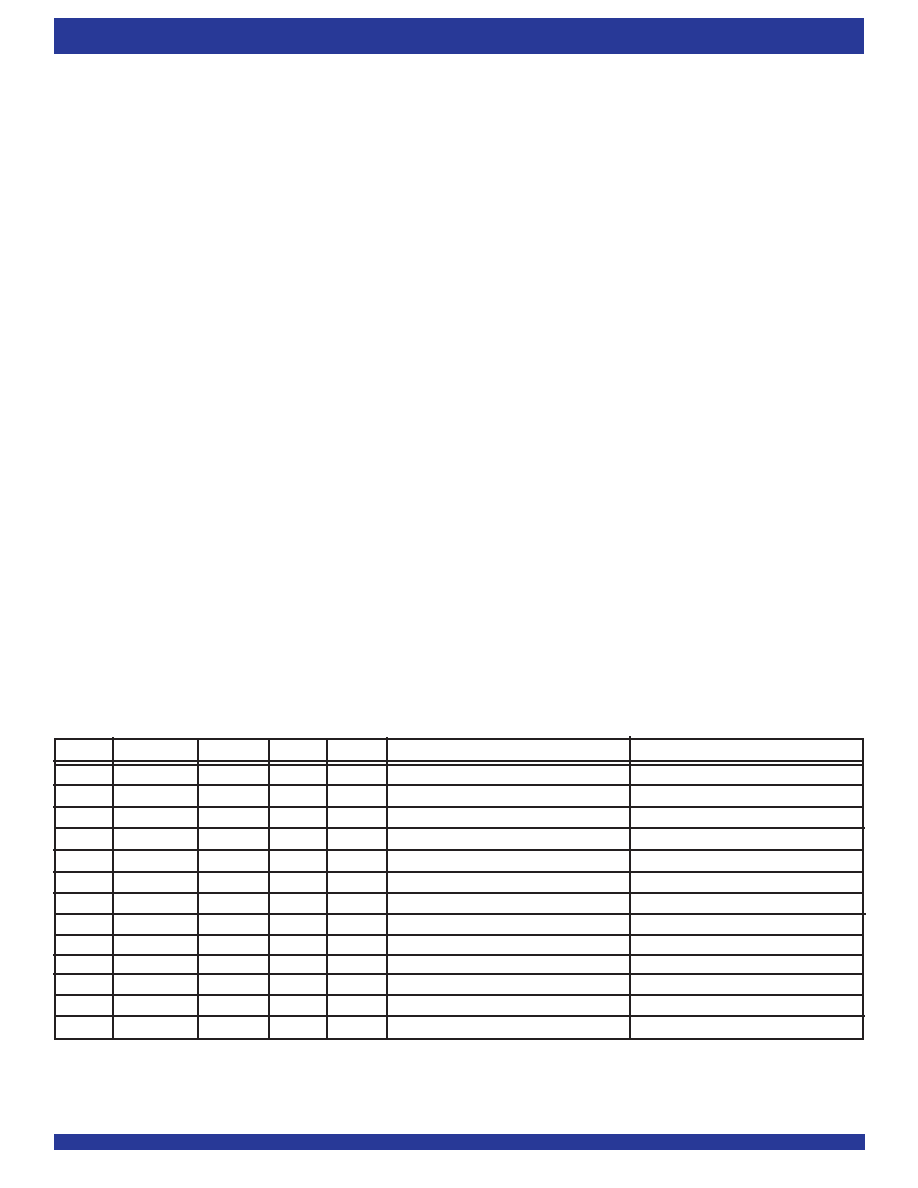

FS2

FS1/

SEN

FS0/SD

MRS1

MRS2

X1 AND Y1 REGlSTERS(1)

X2 AND Y2 REGlSTERS(2)

HH

H

↑

X64

X

HH

H

X

↑

X64

HH

L

↑

X16

X

HH

L

X

↑

X16

HL

H

↑

X8

X

HL

H

X

↑

X8

LH

H

↑

X

256

X

LH

H

X

↑

X

256

LL

H

↑

X

1,024

X

LL

H

X

↑

X

1,024

LH

L

↑↑

Serial programming via SD

HL

L

↑↑

Parallel programming via Port A(3,5)

LL

L

↑↑

IP Mode(4, 5)

Once the Master Reset (

MRS1, MRS2) input is HIGH, a LOW on the BE/

FWFTinputduringthenextLOW-to-HIGHtransitionofCLKA(forFIFO1)and

CLKC (for FIFO2) will select FWFT mode. This mode uses the Output Ready

function (ORA, ORB) to indicate whether or not there is valid data at the data

outputs (A0-A35 or B0-B17). It also uses the Input Ready function (IRA, IRC)

to indicate whether or not the FIFO memory has any free space for writing. In

theFWFTmode,thefirstwordwrittentoanemptyFIFOgoesdirectlytothedata

outputs, no read request necessary. Subsequent words must be accessed by

performing a formal read operation.

Following Master Reset, the level applied to the BE/

FWFT inputtochoose

the desired timing mode must remain static throughout FIFO operation. Refer

to Figure 4 (FIFO1 Master Reset) and Figure 5 (FIFO2 Master Reset) for First

Word Fall Through select timing diagrams.

PROGRAMMING THE ALMOST-EMPTY AND ALMOST-FULL FLAGS

FourregistersintheseFIFOsareusedtoholdtheoffsetvaluesfortheAlmost-

EmptyandAlmost-Fullflags. ThePortBAlmost-Emptyflag(

AEB)Offsetregister

is labeled X1 and the Port A Almost-Empty flag (

AEA)Offsetregisterislabeled

X2. The Port A Almost-Full flag (

AFA)OffsetregisterislabeledY1andthePort

CAlmost-Fullflag(

AFC)OffsetregisterislabeledY2. Theindexofeachregister

namecorrespondstoitsFIFOnumber. TheOffsetregisterscanbeloadedwith

preset values during the reset of a FIFO, programmed in parallel using the

FIFO’s Port A data inputs, or programmed in serial using the Serial Data (SD)

input (see Table 1).

FS0/SD, FS1/

SEN and FS2 function the same way in both IDT Standard

and FWFT modes.

— PRESET VALUES

ToloadaFIFO’sAlmost-EmptyflagandAlmost-FullflagOffsetregisterswith

oneofthefivepresetvalueslistedinTable1,theflagselectinputsmustbeHIGH

or LOW during a master reset. For example, to load the preset value of 64 into

X1andY1,FS0,FS1andFS2mustbeHIGHwhenFlFO1reset(

MRS1)returns

HIGH. Flag Offset registers associated with FIFO2 are loaded with one of the

preset values in the same way with FIFO2 Master Reset (

MRS2) toggled

simultaneously with FIFO1 Master Reset (

MRS1). ForrelevantPresetvalue

loading timing diagrams, see Figure 4 and 5.

— PARALLEL LOAD FROM PORT A

To program the X1, X2, Y1, and Y2 registers from Port A, perform a Master

Reset on both FlFOs simultaneously with FS2 HIGH or LOW, FS0 and FS1

LOWduringtheLOW-to-HIGHtransitionof

MRS1andMRS2. ThestateofFS2

atthispointofresetwilldeterminewhethertheparallelprogrammingmethodhas

Interspersed Parity or Non-Interspersed Parity. Refer to Table 1 for Flag

Programming Flag Offset setup . It is important to note that once parallel

programming has been selected during a Master Reset by holding both FS0

& FS1 LOW, these inputs must remain LOW during all subsequent FIFO

operation. They can only be toggled HIGH when future Master Resets are

performed and other programming methods are desired.

After this reset is complete, the first four writes to FIFO1 do not store data in

RAM but load the Offset registers in the order Y1, X1, Y2, X2. For Non-

InterspersedParitymodethePortAdatainputsusedbytheOffsetregistersare

(A10-A0), (A11-A0), or (A12-A0) for the IDT723656, IDT723666, or

IDT723676, respectively. For Interspersed Parity mode the Port A data inputs

used by the Offset registers are (A11-A9, A7-A0), (A12-A9, A7-A0), or (A13-

A9, A7-A0) for the IDT723656, IDT723666, or IDT723676, respectively. The

highest numbered input is used as the most significant bit of the binary number

ineachcase. Validprogrammingvaluesfortheregistersrangefrom1to2,044

for the IDT723656; 1 to 4,092 for the IDT723666; and 1 to 8,188 for the

IDT723676. AfteralltheOffsetregistersareprogrammedfromPortA,thePort

C Full/Input Ready flag (

FFC/IRC)issetHIGH,andbothFIFOsbeginnormal

operation. Refer to Figure 8 for a timing diagram illustration for parallel

programming of the flag offset values.

INTERSPERSED PARITY

Interspersed Parity is selected during a Master Reset of the FIFO. Refer to

Table 1 for the set-up configuration of Interspersed Parity. The Interspersed

Parity function allows the user to select the location of the parity bits in the word

loadedintotheparallelport(A0-An)duringprogrammingoftheflagoffsetvalues.

TABLE 1 —

—

— FLAG PROGRAMMING

NOTES:

1. X1 register holds the offset for

AEB; Y1 register holds the offset for AFA.

2. X2 register holds the offset for

AEA; Y2 register holds the offset for AFC.

3. When this method of parallel programming is selected, Port A will assume Non-Interspersed Parity.

4. When IP Mode is selected, only parallel programming of the offset values via Port A, can be performed and Port A will assume Interspersed Parity.

5. IF parallel programming is selected during a Master Reset, then FS0 & FS1 must remain LOW during FIFO operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27656T15F15PB | CONN RCPT 15POS WALL MNT W/PINS |

| VE-BWN-MW-F2 | CONVERTER MOD DC/DC 18.5V 100W |

| MAX1082BEUE+T | IC ADC 10BIT 400KSPS 16-TSSOP |

| VE-BWN-MW-F1 | CONVERTER MOD DC/DC 18.5V 100W |

| ISL4485EIBZ-T | IC TXRX 1TX/1RX 5V RS-485 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72401L10DB | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO ASYNC 64X4 16CDIP |

| IDT72401L10P | 功能描述:IC FIFO PAR 64X4 10NS 16-DIP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72401L10SO | 功能描述:IC FIFO PAR 64X4 10NS 16-SOIC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72401L10SO8 | 功能描述:IC FIFO PAR 64X4 10NS 16-SOIC RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72401L15DB | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO ASYNC 64X4 16CDIP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。