- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377254 > IDT7006S35PFB (INTEGRATED DEVICE TECHNOLOGY INC) Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel PDF資料下載

參數(shù)資料

| 型號: | IDT7006S35PFB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel |

| 中文描述: | 16K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, TQFP-64 |

| 文件頁數(shù): | 13/20頁 |

| 文件大?。?/td> | 263K |

| 代理商: | IDT7006S35PFB |

IDT7006S/L

HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

6.07

13

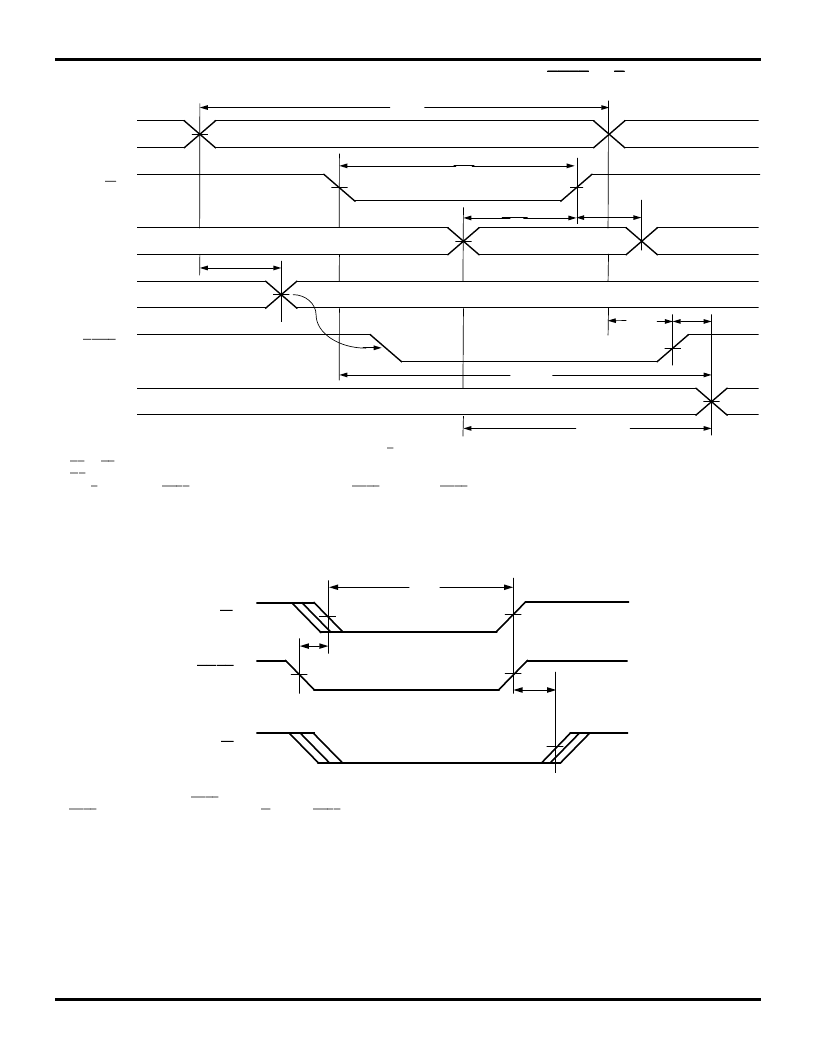

TIMING WAVEFORM OF WRITE WITH PORT-TO-PORT READ AND

BUSY

(M/

S

= V

IH

)

(2,4,5)

TIMING WAVEFORM OF WRITE WITH BUSY

NOTES:

1. tWH must be met for both

BUSY

input (slave) and output (master).

2.

BUSY

is asserted on Port "B" blocking R/

W

"B", until

BUSY

"B" goes High.

3. tWB is only for the 'Slave' Version

.

2739 drw 14

R/

W

"A"

BUSY

"B"

t

WP

t

WB

R/

W

"B"

t

WH

(2)

(3)

(1)

2739 drw 13

t

DW

t

APS

ADDR

"A"

t

WC

DATA

OUT "B"

MATCH

t

WP

R/

W

"A"

DATA

IN "A"

ADDR

"B"

t

DH

VALID

(1)

MATCH

BUSY

"B"

t

BDA

VALID

t

BDD

t

DDD(3)

t

WDD

NOTES:

1. To ensure that the earlier of the two ports wins. t

APS

is ignored for M/

S

=

V

IL (slave).

2.

CE

L

=

CE

R

= V

IL.

3.

OE

= V

IL

for the reading port.

4. If M/

S

= V

IL

(slave),

BUSY

is an input. Then for this example

BUSY

"A"

= V

IH

and

BUSY

"B"

input is shown above.

5. All timing is the same for left and right port. Port "A" may be either left or right port. Port "B" is the port opposite from Port "A".

相關PDF資料 |

PDF描述 |

|---|---|

| IDT7006S55G | Single Synchronous Buck PWM Controller |

| IDT7006S55GB | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Rail |

| IDT7006S55J | Single Synchronous Buck PWM Controller |

| IDT7006S55PF | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel |

| IDT7006S55PFB | Single Synchronous Buck PWM Controller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7006S35XL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S35XLB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45FB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。