- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377242 > IDT6116LA55DB (INTEGRATED DEVICE TECHNOLOGY INC) Enhanced-JFET Low-Power Low-Offset Dual Operational Amplifier 8-SOIC 0 to 70 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT6116LA55DB |

| 廠(chǎng)商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | Enhanced-JFET Low-Power Low-Offset Dual Operational Amplifier 8-SOIC 0 to 70 |

| 中文描述: | 2K X 8 STANDARD SRAM, 55 ns, CDIP24 |

| 封裝: | 0.600 INCH, CERAMIC, DIP-24 |

| 文件頁(yè)數(shù): | 8/10頁(yè) |

| 文件大小: | 91K |

| 代理商: | IDT6116LA55DB |

5.1

8

IDT6116SA/LA

CMOS STATIC RAM 16K (2K x 8-BIT)

MILITARY AND COMMERCIAL TEMPERATURE RANGES

6116SA15

(1)

6116LA15

(1)

Min.

6116SA20

6116LA20

Min.

6116SA25

6116LA25

Min.

6116SA35

6116LA35

Min.

Symbol

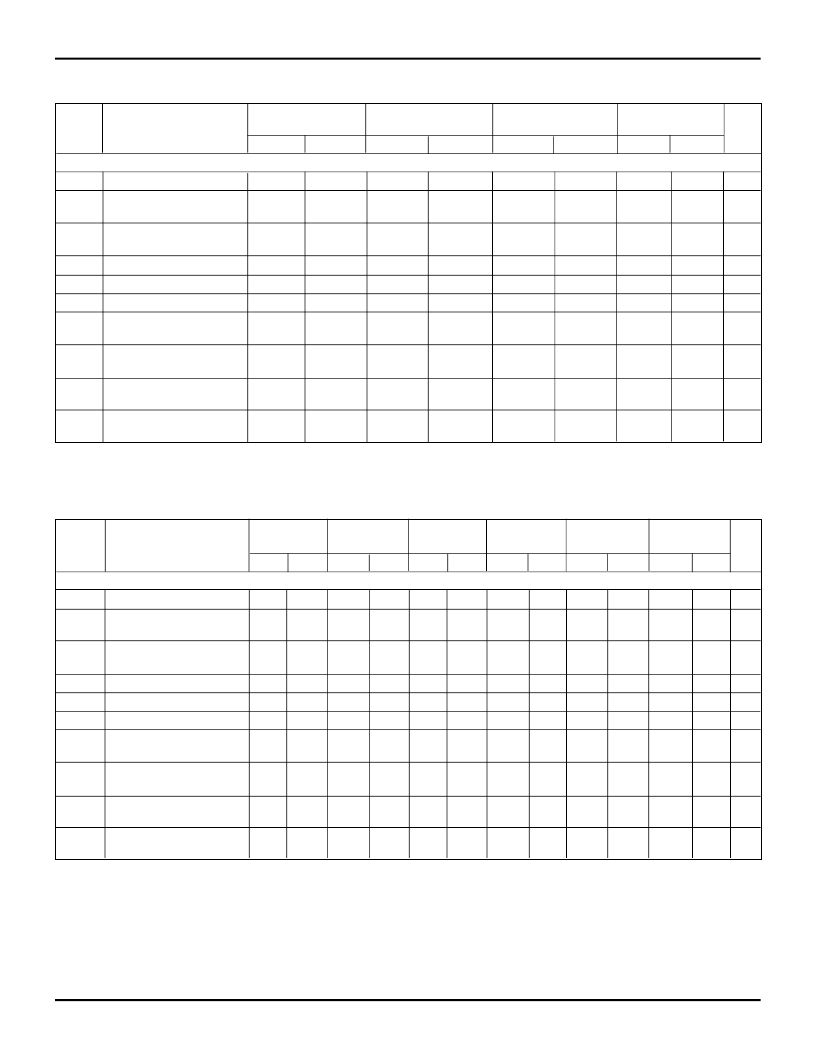

WRITE CYCLE

t

WC

t

CW

Parameter

Max.

Max.

Max.

Max.

Unit

Write Cycle Time

Chip Select to End-of-

Write

Address Valid to End-

of-Write

Address Set-up Time

Write Pulse Width

Write Recovery Time

Write to Output

in High-Z

Data to Write Time

Overlap

Data Hold from Write

Time

Output Active from

End-of-Write

15

13

—

—

20

15

—

—

25

17

—

—

35

25

—

—

ns

ns

t

AW

14

—

15

—

17

—

25

—

ns

t

AS

t

WP

t

WR

t

WHZ

(3)

0

—

—

—

7

0

12

0

—

—

—

—

8

0

15

0

—

—

—

—

16

0

20

0

—

—

—

—

20

ns

ns

ns

ns

12

0

—

t

DW

12

—

12

—

13

—

15

—

ns

t

DH

(4)

0

—

0

—

0

—

0

—

ns

t

OW

(3,4)

0

—

0

—

0

—

0

—

ns

3089 tbl 14

AC ELECTRICAL CHARACTERISTICS

(V

CC

= 5V

±

10%, All Temperature Ranges)

6116SA45

6116LA45

Min.

6116SA55

(2)

6116LA55

(2)

Min.

6116SA70

(2)

6116LA70

(2)

Min. Max.

6116SA90

(2)

6116LA90

(2)

Min.

6116SA120

(2)

6116LA120

(2)

Min.

6116SA150

(2)

6116LA150

(2)

Min.

Symbol

WRITE CYCLE

t

WC

t

CW

Parameter

Max.

Max.

Max.

Max.

Max.

Unit

Write Cycle Time

Chip Select to End of

Write

Address Valid to End

of Write

Address Set-up Time

Write Pulse Width

Write Recovery Time

Write to Output

in High-Z

Data to Write Time

Overlap

Data Hold from Write

Time

Output Active from

End of Write

45

30

—

—

55

40

—

—

70

40

—

—

90

55

—

—

120

70

—

—

150

90

—

—

ns

ns

t

AW

30

—

45

—

65

—

80

—

105

—

120

—

ns

t

AS

t

WP

t

WR

t

WHZ

(3)

0

—

—

—

25

5

40

5

—

—

—

—

30

15

40

5

—

—

—

—

35

15

55

5

—

—

—

—

40

20

70

5

—

—

—

—

40

20

90

10

—

—

—

—

40

ns

ns

ns

ns

25

0

—

t

DW

20

—

25

—

30

—

30

—

35

—

40

—

ns

t

DH

(4)

0

—

5

—

5

—

5

—

5

—

10

—

ns

t

OW

(3,4)

0

—

0

—

0

—

0

—

0

—

0

—

ns

NOTES:

1. 0

°

C to +70

°

C temperature range only.

2. –55

°

C to +125

°

C temperature range only.

3. This parameter guaranteed with AC Load (Figure 2) by device characterization, but is not production tested.

4. The specification for t

DH

must be met by the device supplying write data to the RAM under all operation conditions. Although t

DH

and t

OW

values will vary

over voltage and temperature, the actual t

DH

will always be smaller than the actual t

OW

.

3089 tbl 15

AC ELECTRICAL CHARACTERISTICS

(V

CC

= 5V

±

10%, All Temperature Ranges)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT6116LA55P | Enhanced-JFET Low-Power Low-Offset Dual Operational Amplifier 8-SOIC 0 to 70 |

| IDT6116LA55PB | Enhanced-JFET Low-Power Low-Offset Dual Operational Amplifier 8-SOIC 0 to 70 |

| IDT6116SA15D | Quad Enhanced JFET Low-Power Precision Operational Amplifier 14-TSSOP 0 to 70 |

| IDT6116SA15DB | Quad Enhanced JFET Low-Power Precision Operational Amplifier 14-TSSOP 0 to 70 |

| IDT6116SA15P | CMOS STATIC RAM 16K (2K x 8 BIT) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT6116LA55L24B | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:x8 SRAM |

| IDT6116LA55P | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116LA55PB | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116LA55SO | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (2K x 8 BIT) |

| IDT6116LA55SOB | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:CMOS STATIC RAM 16K (2K x 8 BIT) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。