- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSSSTUA32866BHLFT SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 PDF資料下載

參數(shù)資料

| 型號(hào): | ICSSSTUA32866BHLFT |

| 元件分類: | 鎖存器 |

| 英文描述: | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| 封裝: | 5.50 X 13.50 MM, LEAD FREE, MO-205, LFBGA-96 |

| 文件頁(yè)數(shù): | 14/27頁(yè) |

| 文件大小: | 307K |

| 代理商: | ICSSSTUA32866BHLFT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

21

ICSSSTUA32866B

1054A—01/28/05

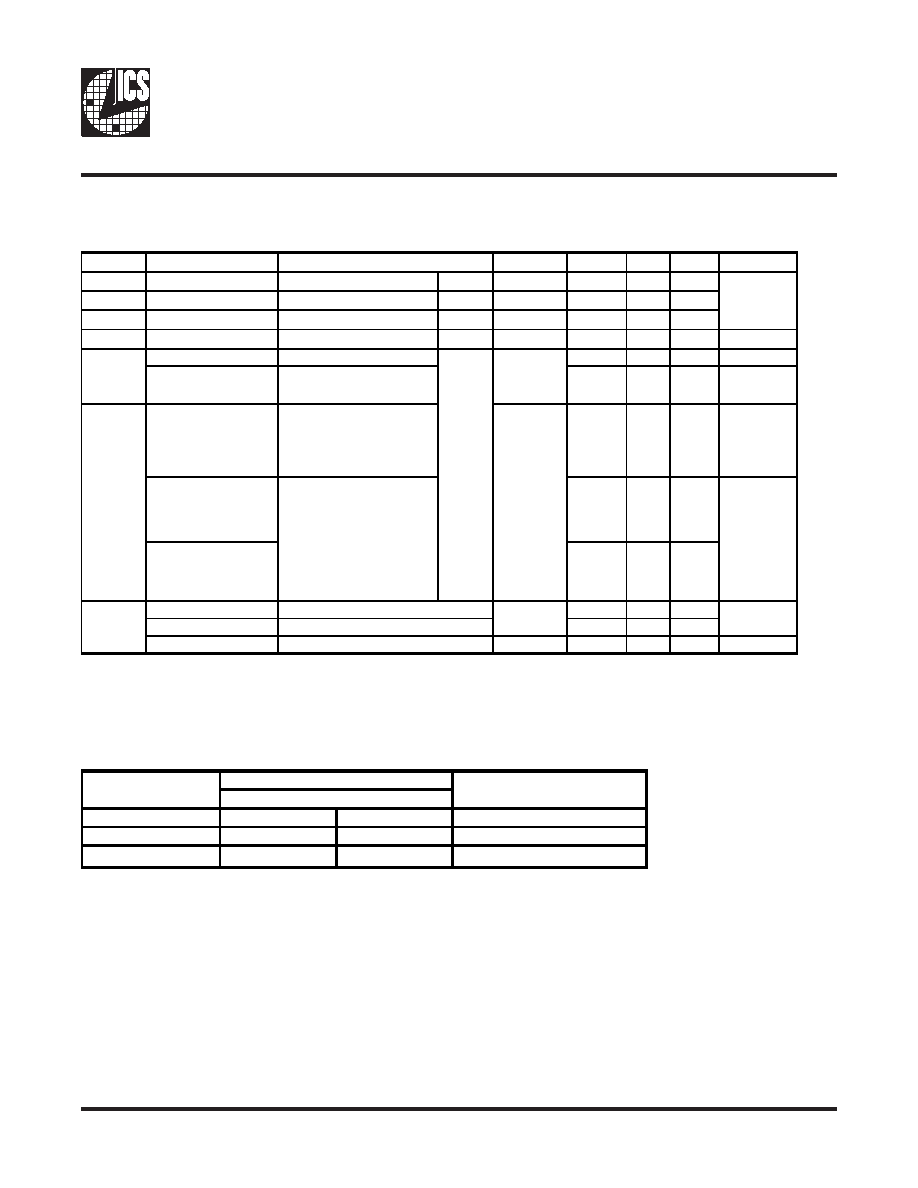

Electrical Characteristics - DC

TA = 0 - 70°C; VDD = 1.8 +/-0.1V (unless otherwise stated)

SYMBOL

PARAMETERS

VDD

MIN

TYP

MAX

UNITS

VIK

II = -18mA

-1.2

VOH

IOH = -6mA

1.7V

1.2

VOL

IOL = 6mA

1.7V

0.5

II

All Inputs

VI = VDD or GND

1.9V

-5

5

A

Standby (Static)

RESET# = GND

100

A

Operating (Static)

VI = VIH(AC) or VIL(AC),

RESET# = VDD

40

mA

Dynamic operating

(clock only)

RESET# = VDD,

VI = VIH(AC) or VIL(AC),

CLK and CLK# switching

50% duty cycle.

39

/clock

MHz

Dynamic Operating

(per each data input)

1:1 mode

19

Dynamic Operating

(per each data input)

1:2 mode

35

Data Inputs

2.5

3.5

CLK and CLK#

2

3

RESET#

2.5

Notes:

1 - Guaranteed by design, not 100% tested in production.

pF

VICR = 1.25V, VI(PP) = 360mV

VI = VDD or GND

CONDITIONS

V

A/ clock

MHz/data

Ci

VI = VREF ±350mV

IDD

IO = 0

1.9V

IDDD

1.8V

RESET# = VDD,

VI = VIH(AC) or VIL (AC),

CLK and CLK# switching

50% duty cycle. One data

input switching at half

clock frequency, 50%

duty cycle

Output Buffer Characteristics

Output edge rates over recommended operating free-air temperature range (See figure 7)

MIN

MAX

dV/dt_r

1

4

V/ns

dV/dt_f

1

4

V/ns

dV/dt_

1

1V/ns

1. Difference between dV/dt_r (rising edge rate) and dV/dt_f (falling edge rate)

PARAMETER

VDD = 1.8V ± 0.1V

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSSSTUA32S865AH-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| ICSSSTUA32S865AHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| ICSSSTUB32871AHMLFT | 32871 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYH-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTUA32S869B | 制造商:ICS 制造商全稱:ICS 功能描述:14-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUAF32865A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32865AHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866B | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866BHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。