- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSS98UAE877AKLFT (INTEGRATED DEVICE TECHNOLOGY INC) 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | ICSS98UAE877AKLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 98UAE SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 封裝: | 6 X 6 MM, LEAD FREE, PLASTIC, MLF-40 |

| 文件頁(yè)數(shù): | 16/18頁(yè) |

| 文件大小: | 331K |

| 代理商: | ICSS98UAE877AKLFT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)

ICS98UAE877A

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

COMMERCIAL TEMPERATURE GRADE

1.5V LOW-POWER WIDE-RANGE FREQUENCY CLOCK DRIVER

7

ICS98UAE877A

7181/2

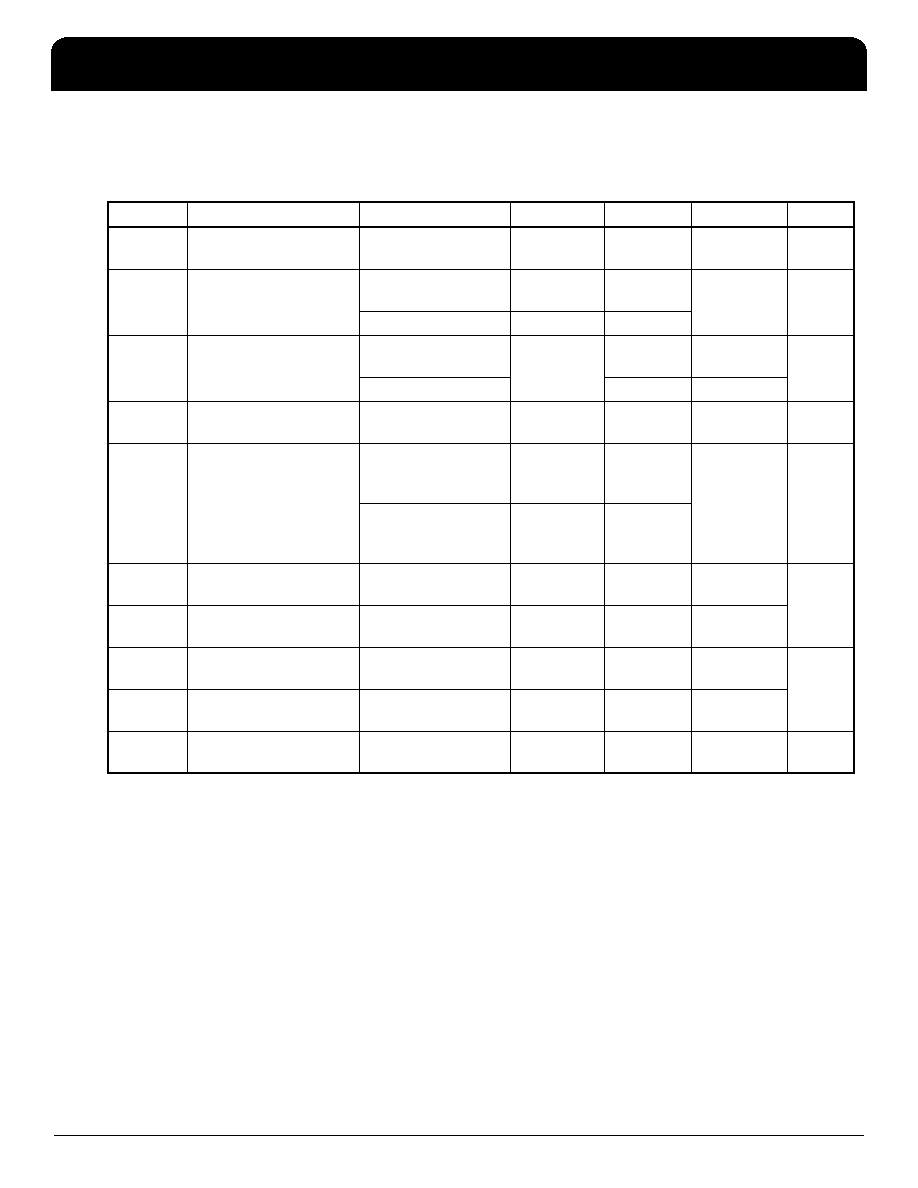

Recommended Operating Conditions

Following Conditions Apply Unless Otherwise Specified:

Commercial: TA = 0°C to +70°C, Industrial: TA = -40°C to +85°C; Supply Voltage AVDD/VDDQ = 1.5V ± 0.075V.

Symbol

Parameter1

1

Unused inputs must be held HIGH or LOW to prevent them from floating.

Conditions

Min.

Typ.

Max.

Units

AVDD,

VDDQ

Supply Voltage

1.425

1.5

1.575

V

VIL

LOW - Level Input

Voltage

CLK_INT, CLK_INC,

FB_INT, FB_INC

0.35 x VDDQ

V

OE, OS

VIH

HIGH -Level Input

Voltage

CLK_INT, CLK_INC,

FB_INT, FB_INC

0.65 x VDDQ

V

OE, OS

VIN

DC Input Signal

Voltage2

2

DC input signal voltage specifies the allowable DC execution of differential input.

-0.3

VDDQ + 0.3

V

VID

Differential Input Signal

Voltage3

3

Differential inputs signal voltages specifies the differential voltage [VTR-VCP] required for switching,

where VTR is the true input level and VCP is the complementary input level.

DC - CLK_INT,

CLK_INC, FB_INT,

FB_INC

0.35

VDDQ + 0.4

V

AC - CLK_INT,

CLK_INC, FB_INT,

FB_INC

0.6

VOX

Output Differential

Cross-Voltage4

4

Differential cross-point voltage is expected to track variations of VDDQ and is the voltage at which the

differential signal must be crossing.

VDDQ/2 - 0.1

VDDQ/2 +0.1

V

VIX

Input Differential

Cross-Voltage4

VDDQ/2 -

0.15

VDDQ/2

VDDQ/2 +

0.15

IOH

HIGH-Level Output

Current

-6

mA

IOL

LOW-Level Output

Current

6

TA

Operating Free-Air

Temperature

-40

+85

°C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSSSTU3286AHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32864BHMLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32866BHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUA32S865AH-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTU32864 | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer |

| ICSSSTUA32S869B | 制造商:ICS 制造商全稱:ICS 功能描述:14-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUAF32865A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32865AHLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866B | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。