- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360784 > ICS9248YF-96LF-T Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ PDF資料下載

參數(shù)資料

| 型號(hào): | ICS9248YF-96LF-T |

| 英文描述: | Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| 中文描述: | 頻率發(fā)生器 |

| 文件頁(yè)數(shù): | 8/12頁(yè) |

| 文件大?。?/td> | 206K |

| 代理商: | ICS9248YF-96LF-T |

8

ICS9248-96

0311D—04/23/04

Absolute Maximum Ratings

Core Supply Voltage . . . . . . . . . . . . . . . . . . . . 4.6 V

I/O Supply Voltage . . . . . . . . . . . . . . . . . . . . . 3.6V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . GND –0.5 V to V

DD

+0.5 V

Ambient Operating Temperature . . . . . . . . . . 0°C to +70°C

Storage Temperature. . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Stresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. These

ratings are stress specifications only and functional operation of the device at these or any other conditions above those

listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect product reliability.

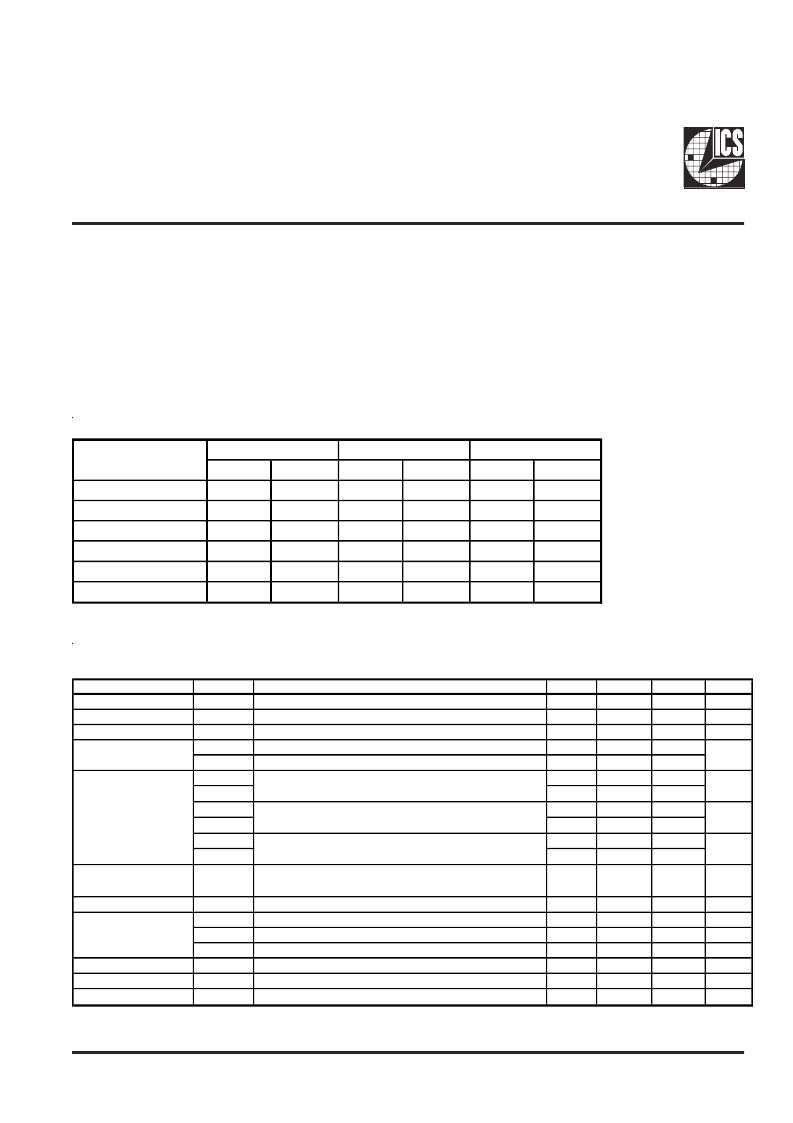

Group Timing Relationship Table

Group

Offset

2.5ns

7.5ns

0.0ns

1.5-3.5ns

0.0ns

Async

Tolerance

500ps

500ps

500ps

500ps

1.0ns

N/A

Offset

5.0ns

5.0ns

0.0ns

1.5-3.5ns

0.0ns

Async

Tolerance

500ps

500ps

500ps

500ps

1.0ns

N/A

Offset

0.0ns

0.0ns

0.0ns

1.5-3.5ns

0.0ns

Async

Tolerance

500ps

500ps

500ps

500ps

1.0ns

N/A

CPU to SDRAM

CPU to 3V66

SDRAM to 3V66

3V66 to PCI

PCI to PCI

USB & DOT

CPU 133MHz

CPU 66MHz

CPU 100MHz

Electrical Characteristics - Input/Supply/Common Output Parameters

T

A

= 0 - 70°C; Supply Voltage V

DD

= 3.3 V +/-5%, V

DDL

= 2.5 V +/-5% (unless otherwise stated)

PARAMETER

SYMBOL

Input High Voltage

V

IH

Input Low Voltage

V

IL

Input High Current

I

IH

V

IN

= V

DD

I

IL1

V

IN

= 0 V; Inputs with no pull-up resistors

I

IL2

V

IN

= 0 V; Inputs with pull-up resistors

I

DD3.3OP

I

DD2.5OP

I

DD3.3OP

I

DD2.5OP

I

DD3.3OP

I

DD2.5OP

Power Down Supply

Current

CONDITIONS

MIN

2

TYP

MAX

V

DD

+ 0.3

0.8

5

UNITS

V

V

mA

V

SS

- 0.3

-5

-5

-200

300

12

300

25

300

35

340

15

350

30

420

40

Input Frequency

F

i

C

IN

C

OUT

C

INX

T

trans

T

s

T

STAB

V

DD

= 3.3 V

Logic Inputs

Output pin capacitance

X1 & X2 pins

To 1st crossing of target frequency

From 1st crossing to 1% target frequency

From V

DD

= 3.3 V to 1% target frequency

14.31818

MHz

pF

pF

pF

ms

ms

ms

5

6

45

3

3

3

27

Transition time

1

Settling time

1

Clk Stabilization

1

1

Guaranteed by design, not 100% tested in production.

300

I

DD3.3PD

C

L

= Max loads; V

IN

= V

DD

or GND

Input Capacitance

1

Input Low Current

C

L

= Max loads; CPU @ 66 MHz; SDRAM @ 100 MHz

C

L

= Max loads; CPU @ 100 MHz; SDRAM @ 100 MHz

C

L

= Max loads; CPU @ 133 MHz; SDRAM @ 133 MHz

Operating Supply

Current

600

mA

μ

A

mA

mA

mA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS9248YF-96-T | Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS932S202 | Frequency Timing Generator for Differential PIIIType Dual-CPU Systems |

| ICS932S208 | Programmable Timing Control Hub⑩ for Next Gen P4⑩ processor |

| ICS932S208YFLF-T | Programmable Timing Control Hub⑩ for Next Gen P4⑩ processor |

| ICS932S208YGLF-T | Programmable Timing Control Hub⑩ for Next Gen P4⑩ processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS9248YF-96-T | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9248YF-97-T | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Timing Generator for PENTIUM II Systems |

| ICS9248YF-98-T | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9248YF-99 | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Generator & Integrated Buffers for Celeron & PII/III⑩ |

| ICS9248YG-101-T | 制造商:ICS 制造商全稱(chēng):ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM & K6 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。